Experimental Board 1.3 for Series 1 FPGA Boards

Series 1 FPGA Boards are deprecated. Please switch to Series 2.

The old product page is still available here for documentation purposes.

|

Features Additional resources |

|

Features

- Baseboard for USB-FPGA Modules 1.2, 1.11 and 1.15.

- High-efficiency switching regulators to generate the supply voltages

- 1.2 V @ 8 A

- 2.6 V @ 2.5 A

- 3.3 V @ 2.5 A

- Wide input range: 4.5 to 16 V

- I/O voltages VCCO_RIGHT / VCCO_IO and VCCO_TOP can be easily and independently set to 3.3V, 2.6V, 1.2V or to an external voltage.

- All I/O Ports available on a standard 2.54 mm (0.1 inch) grid via six 1x23 pin connectors to which Expansion Boards or Breadboards can be connected

- Downward pin compatible to Experimental Board 1.2 and Experimental Board 1.1

- JTAG interface for the FPGA

Functional description

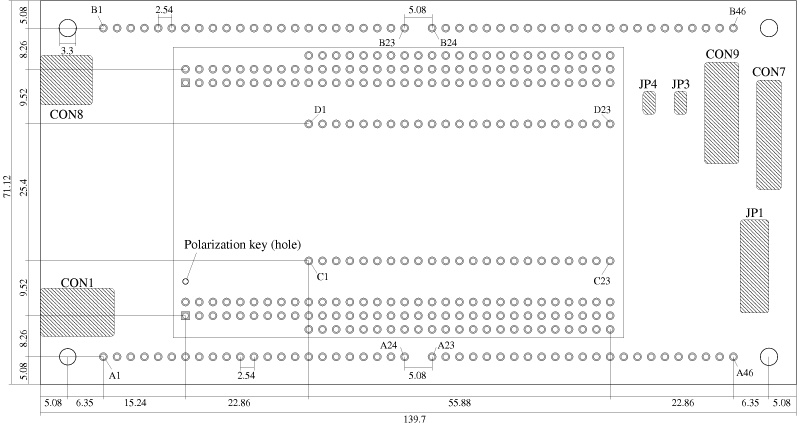

The following drawing shows the measurements and the location of the of the described elements.

Click on the image for a larger version or download the PDF version.

External power: CON1 and CON8

CON1 is a standard DC power jack with 2.1mm center pin (+) diameter and 5.5mm barrel (-) diameter for a supply voltage of 4.5 V to 16 V.Alternatively CON8 can be used to connect non standard power cables. The ground pin of CON8 (round pad) is marked with "-" and the supply pin (quadratic pad) is marked with "+", see the images below.

It is also possible to supply the external voltage via the Vin pin of the Experimental Board I/O Connector described below.

If non-stabilized power supplies are used it must be made sure that the peak voltage is not larger then 18V.

Hints for power supply via USB can be found on the ZTEX Wiki.

JTAG connector: CON7, CON9, JP3 and JP4

The Experimental Board contains two JTAG connectors. CON9 is a 14 pin, 2.0mm pitch connector standardized by Xilinx. CON7 can be used to connect non-standard JTAG programmers.The pin descriptions can be found in the silk screen (see the images).

The voltage for the I/O signals (TCK,TMS,TDI,TDO) is 2.6V. The supply pin of this voltage is labelled with "VIO". The "3V3" pin to CON7 can be used as 3.3V supply for the JTAG adapter.

On USB-FPGA Modules 1.2 jumpers JP3 and JP4 can be closed to enforce JTAG configuration mode. But usually this is not required since the JTAG interface is always enabled. On Spartan 6 USB-FPGA Modules 1.11 and 1.15 these jumpers have no function.

I/O voltages: JP1

Jumper JP1 sets the I/O VCCO_IO(=VCCO_RIGHT) and VCCO_TOP, respectively.On Spartan 6 USB-FPGA Modules 1.11 and 1.15 V_TOP has no function. (The I/O voltage of the pins at rows C,D and F of the I/O Connector is fixed to 3.3V.)

By closing this jumpers (see images below) the I/O voltages can be switched easily to 3.3V, 2.6V or 1.2V. If other I/O voltages are required the jumpers must be left open and the I/O voltage must be supplied via th VIO or VT pins of the Experimental Board I/O Connector, respectively.

Experimental Board I/O Connector

Six 1x23 pin connectors deliver I/O signals and voltages to user circuits. This I/O connectors is downward compatible with Experimental Boards 1.2 and 1.1.

The drawing shows the position of the connectors.

The Pinlist and the List of Connections are can be downloaded in Gnumeric or Excel format. The following table is is a short version the these files:

| Experimental Board 1.3 | USB-FPGA Modules | ||||||||||

| I/O Con. | EZ-USB FX2 pin | FPGA pin | |||||||||

| Pin | Pin name | Pin | -100 | -128 | 1.2 | 1.11 | 1.15 | ||||

| A1 | Vin | A1, B1 | |||||||||

| A2 | 3V3 | ||||||||||

| A3 | GND | ||||||||||

| A4 | A3 | A3 | 22 | 28 | C18 | ||||||

| A5 | B3 | B3 | 23 | 29 | |||||||

| A6 | A4 | A4 | 24 | 30 | |||||||

| A7 | SCL | A6 | 29 | 36 | F22 | ||||||

| A8 | SDA | B6 | 30 | 37 | E22 | ||||||

| A9 | GND | B13 | |||||||||

| A10 | VIO | ||||||||||

| A11 | B12 | B12 | 73 | B14 | B18 | ||||||

| A12 | A12 | A12 | 74 | A14 | A18 | ||||||

| A13 | A13 | A13 | 76 | C13 | D17 | ||||||

| A14 | B14 | B14 | 77 | D11 | C17 | ||||||

| A15 | A14 | A14 | 78 | D12 | A17 | ||||||

| A16 | B15 | B15 | 79 | F10 | D15 | ||||||

| A17 | A15 | A15 | 80 | E11 | C14 | ||||||

| A18 | B17 | B17 | 82 | E10 | C11 | ||||||

| A19 | A17 | A17 | 83 | C10 | A11 | ||||||

| A20 | B25 | B25 | 95 | F7 | D9 | ||||||

| A21 | A18 | A18 | 85 | B12 | C13 | ||||||

| A22 | B19 | B19 | 86 | C9 | D11 | ||||||

| A23 | A19 | A19 | 87 | A9 | C12 | ||||||

| A24 | B20 | B20 | 89 | D8 | F10 | ||||||

| A25 | A20 | A20 | 90 | C8 | C15 | ||||||

| A26 | VIO | ||||||||||

| A27 | GND | ||||||||||

| A28 | B24 | B24 | 92 | C7 | D10 | ||||||

| A29 | A24 | A24 | 93 | A7 | C10 | ||||||

| A30 | B18 | B18 | 84 | A12 | A13 | ||||||

| A31 | A25 | A25 | 96 | E6 | D8 | ||||||

| A32 | B26 | B26 | 97 | D6 | B8 | ||||||

| A33 | A26 | A26 | 98 | C6 | A8 | ||||||

| A34 | B27 | B27 | 99 | B6 | D7 | ||||||

| A35 | A27 | A27 | 100 | A6 | C8 | ||||||

| A36 | B28 | B28 | 102 | D5 | D6 | ||||||

| A37 | A28 | A28 | 103 | C5 | C6 | ||||||

| A38 | B29 | B29 | 104 | B5 | C5 | ||||||

| A39 | A29 | A29 | 105 | A5 | A5 | ||||||

| A40 | B30 | B30 | 107 | C4 | A6 | ||||||

| A41 | A30 | A30 | 108 | A4 | B3 | ||||||

| A42 | GND | ||||||||||

| A43 | 3V3 | ||||||||||

| A44 | VIO | ||||||||||

| A45 | 2V5 | ||||||||||

| A46 | 1V2 | ||||||||||

| B1 | 5V | C2, D2 | |||||||||

| B2 | U5V | D1, C1 | |||||||||

| B3 | 3V3 | ||||||||||

| B4 | GND | ||||||||||

| B5 | CLK | C3 | 52 | R16 | L20 | ||||||

| B6 | C5 | C5 | 84 | 106 | V17 | ||||||

| B7 | D8 | D8 | 5 | K16 | V20 | ||||||

| B8 | C9 | C9 | 93 | 115 | |||||||

| B9 | D9 | D9 | 4 | L16 | Y22 | ||||||

| B10 | C10 | C10 | 92 | 114 | |||||||

| B11 | D10 | D10 | 2 | M16 | AA22 | ||||||

| B12 | C11 | C11 | 91 | 113 | |||||||

| B13 | D11 | D11 | 1 | P16 | Y21 | ||||||

| B14 | C12 | C12 | 90 | 112 | |||||||

| B15 | GND | ||||||||||

| B16 | VT | ||||||||||

| B17 | D12 | D12 | 141 | P15 | W20 | ||||||

| B18 | C13 | C13 | 89 | 111 | |||||||

| B19 | D13 | D13 | 140 | T15 | AA20 | ||||||

| B20 | C14 | C14 | 88 | 119 | |||||||

| B21 | D14 | D14 | 137 | K15 | V19 | ||||||

| B22 | C15 | C15 | 87 | 109 | |||||||

| B23 | D15 | D15 | 135 | R14 | Y19 | ||||||

| B24 | C16 | C16 | 86 | 108 | |||||||

| B25 | D16 | D16 | 132 | M13 | V18 | ||||||

| B26 | VT | ||||||||||

| B27 | GND | ||||||||||

| B28 | D17 | D17 | 131 | M12 | Y15 | ||||||

| B29 | D19 | D19 | 130 | T12 | V15 | ||||||

| B30 | D20 | D20 | 129 | R9 | W15 | ||||||

| B31 | C20 | C20 | 128 | P8 | Y11 | ||||||

| B32 | D21 | D21 | 127 | N9 | AA14 | ||||||

| B33 | C21 | C21 | 125 | M9 | AA12 | ||||||

| B34 | D22 | D22 | 124 | N8 | AB12 | ||||||

| B35 | C22 | C22 | 123 | T7 | Y10 | ||||||

| B36 | D23 | D23 | 122 | P7 | AA10 | ||||||

| B37 | C23 | C23 | 119 | M7 | AB10 | ||||||

| B38 | D24 | D24 | 118 | P6 | T14 | ||||||

| B39 | C24 | C24 | 116 | N6 | Y13 | ||||||

| B40 | D25 | D25 | 113 | P4 | W12 | ||||||

| B41 | C25 | C25 | 112 | M6 | W9 | ||||||

| B42 | GND | ||||||||||

| B43 | 3V3 | ||||||||||

| B44 | VT | ||||||||||

| B45 | 2V5 | ||||||||||

| B46 | 1V2 | ||||||||||

| C1 | B4 | B4 | 25 | 31 | |||||||

| C2 | A8 | A8 | 40 | 50 | |||||||

| C3 | B8 | B8 | 41 | 51 | |||||||

| C4 | A9 | A9 | B15 | A20 | |||||||

| C5 | B9 | B9 | B16 | A19 | |||||||

| C6 | E13 | E13 | A13 | C16 | |||||||

| C7 | E14 | E14 | C11 | B16 | |||||||

| C8 | E15 | E15 | A11 | A16 | |||||||

| C9 | E16 | E16 | B10 | B12 | |||||||

| C10 | E17 | E17 | A10 | A12 | |||||||

| C11 | E18 | E18 | F9 | B14 | |||||||

| C12 | E19 | E19 | D9 | A14 | |||||||

| C13 | E20 | E20 | A8 | D12 | |||||||

| C14 | E21 | E21 | B8 | D13 | |||||||

| C15 | E22 | E22 | E8 | A10 | |||||||

| C16 | E23 | E23 | E7 | B10 | |||||||

| C17 | VRI | E12,E28 | |||||||||

| C18 | A5 | A5 | 28 | 34 | |||||||

| C19 | E24 | E24 | C9 | ||||||||

| C20 | E25 | E25 | C7 | ||||||||

| C21 | E26 | E26 | A7 | ||||||||

| C22 | E27 | E27 | B6 | ||||||||

| C23 | VRI | E12,E28 | |||||||||

| D1 | F10 | F10 | N16 | AA21 | |||||||

| D2 | F11 | F11 | M15 | AB21 | |||||||

| D3 | F12 | F12 | R15 | Y20 | |||||||

| D4 | F13 | F13 | L14 | AB20 | |||||||

| D5 | F14 | F14 | N14 | AB19 | |||||||

| D6 | F15 | F15 | L13 | AB18 | |||||||

| D7 | F16 | F16 | L12 | AA18 | |||||||

| D8 | F17 | F17 | R12 | AA16 | |||||||

| D9 | F18 | F18 | M11 | AB15 | |||||||

| D10 | F19 | F19 | M10 | W14 | |||||||

| D11 | F20 | F20 | T9 | Y16 | |||||||

| D12 | F21 | F21 | P9 | AB14 | |||||||

| D13 | F22 | F22 | T8 | AB11 | |||||||

| D14 | F23 | F23 | R7 | W11 | |||||||

| D15 | F24 | F24 | T6 | U14 | |||||||

| D16 | F25 | F25 | T4 | Y12 | |||||||

| D17 | VR3 | F26,F32 | |||||||||

| D18 | F27 | F27 | Y8 | ||||||||

| D19 | F28 | F28 | AB7 | ||||||||

| D20 | F29 | F29 | Y7 | ||||||||

| D21 | F30 | F30 | AB6 | ||||||||

| D22 | F31 | F31 | AA6 | ||||||||

| D23 | VR3 | F26,F32 | |||||||||

PMOD connectors

PMOD modules can be connected directly to the following positions of the Experimental Board I/O connector:- A26 - A31

- A43 - A38

- B43 - B38

- B26 - B31

- B16 - B11

Compatibility notes

The Experimental Board 1.3 is fully downward compatible to the Experimental Board 1.2.Users switching from Experimental Board 1.1 have to consider the following differences:

- The Experimental Board 1.3 does not contain serial drivers anymore. The serial port signals form the EZ-USB FX2 are now available on pins C2 to C5 of the Experimental Board I/O Connector

- Functions of pins A20 and A30 have been swapped.

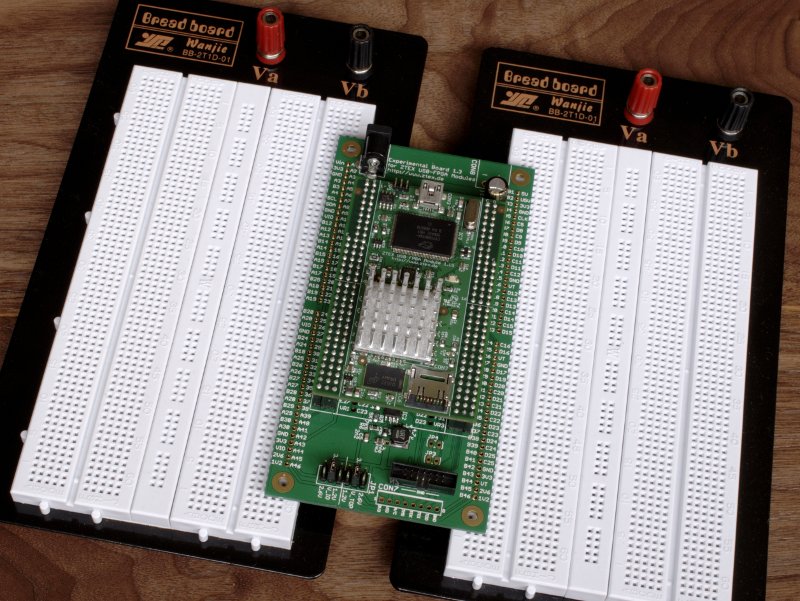

Images

Click on the images for larger versions.

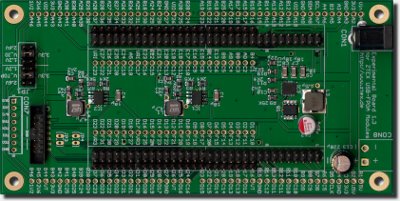

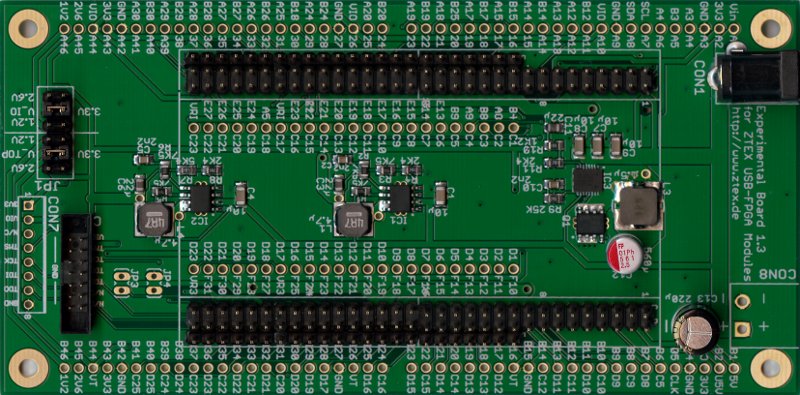

Development Board / Experimental Board 1.3. |

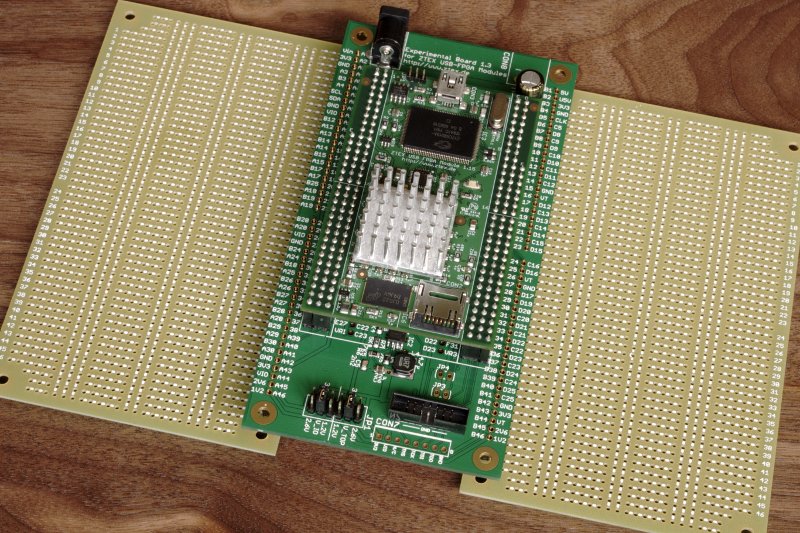

Experimental Board with Spartan 6 LX45 to LX150 USB-FPGA Module 1.15 and two Expansion Boards.

|

Experimental Board with Spartan 6 LX45 to LX150 USB-FPGA Module 1.15 and two Breadboards.

|