USB-FPGA-Modul 1.15y:

Quad-Spartan LX150 FPGA-Board mit USB 2.0-Mikrocontroller

USB-FPGA-Module 1.15y sind veraltet. Bitte wechseln Sie zu FPGA Boards der Serie 2.

Die alte Produktseite ist hier weiterhin zu Dokumentationszwecken verfügbar.

|

Das USB-FPGA-Modul 1.15y beinhaltet vier Spartan 6 XC6SLX150 FPGA's, On-Board Schaltregler und einen USB-Controller. Es ist für Berechnungen optimiert welche wenig Bandbreite und Speicher benötigen. Das FPGA-Board kann zum Bau kostengünstiger FPGA-Cluster mittels Standard-Komponenten verwendet werden.

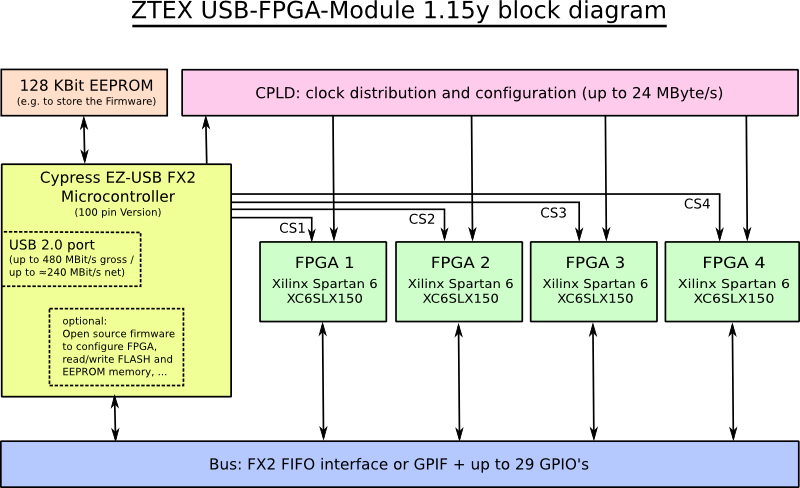

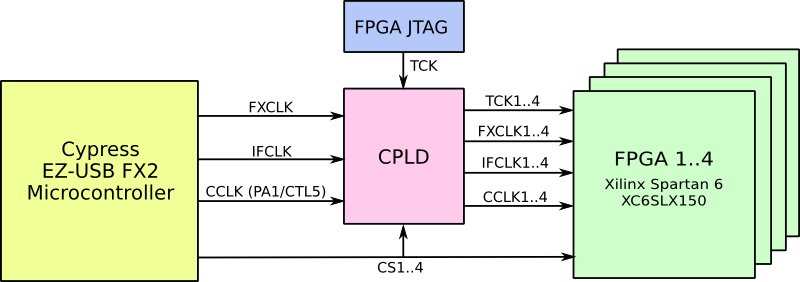

Blockdiagramm

Schaltplan (rev. 1, PDF) |

|

Blockdiagramm

Eigenschaften

- Vier Xilinx Spartan 6 LX150 (XC6SLX150) FPGA, Speedgrade 3N

- High-Speed (480 MBit/s) USB-Interface via Mini-USB-Buchse (Typ B)

- Cypress CY7C68013A EZ-USB FX2 Mikrocontroller

- 128 Kbit EEPROM-Speicher (kann zum Laden der Firmware genutzt werden)

- 2 Kbit MAC-EEPROM: enthält eindeutige, nicht löschbare MAC-Adresse

- Hocheffiziente On-Board Stromversorgung:

- Großer Eingangs-Bereich: 4.5 V - 16 V

- 3,5 V @ 2,5 A

- 4 x 1,2 V @ 8 A

- On-Board-Temperatur-Sensoren (ab Rev. 2)

- Großer Kühlkörper für aktive oder passive Kühlung

- Schnelle FPGA-Konfiguration mittels CPLD: 24 MByte/s via USB

- FPGA-Konfiguration / -Programmierung via USB mittels des EZ-USB FX2 SDK. (Keine JTAG-Adapter oder andere zusätzliche Hilfsmittel erforderlich.)

- Kostenpflichtige ISE Lizenz oder Test-Lizenz für FPGA-Entwicklung erforderlich

Anwendungen

Das FPGA-Board ist für Berechnungen optimiert, welche wenig Bandbreite und Speicher benötigen, wie z.B.:- Bitcoin-Mining

- Monte-Carlo-Simulationen

- Berechnung von Rainbow-Tables

- Brute-Force-Algorithmen

- Bioinformatische Algorithmen

SDK, Beispiele, Tutorials

Für das USB-FPGA-Board steht ein quelloffenes Firmware-Entwicklungskit mit plattform-unabhängiger Hostsoftware API zur Verfügung. Dieses SDK erlaubt die Festlegung der USB-Geräte-Deskriptoren mit nur wenigen Makro-Kommandos und ermöglicht so dem Entwickler einen schnellen Einstieg in die Firmware Programmierung.Das SDK-Paket enthält eine Vielzahl von Beispielen welche als Ausgangspunkt für eigene Entwicklungen genutzt werden können.

Für mehr Informationen wird auf Abschnitt EZ-USB FX2 SDK verwiesen.

Weitere Dokumentationen einschließlich Tutorials befinden sich auf der ZTEX Wiki.

Funktions-Beschreibung

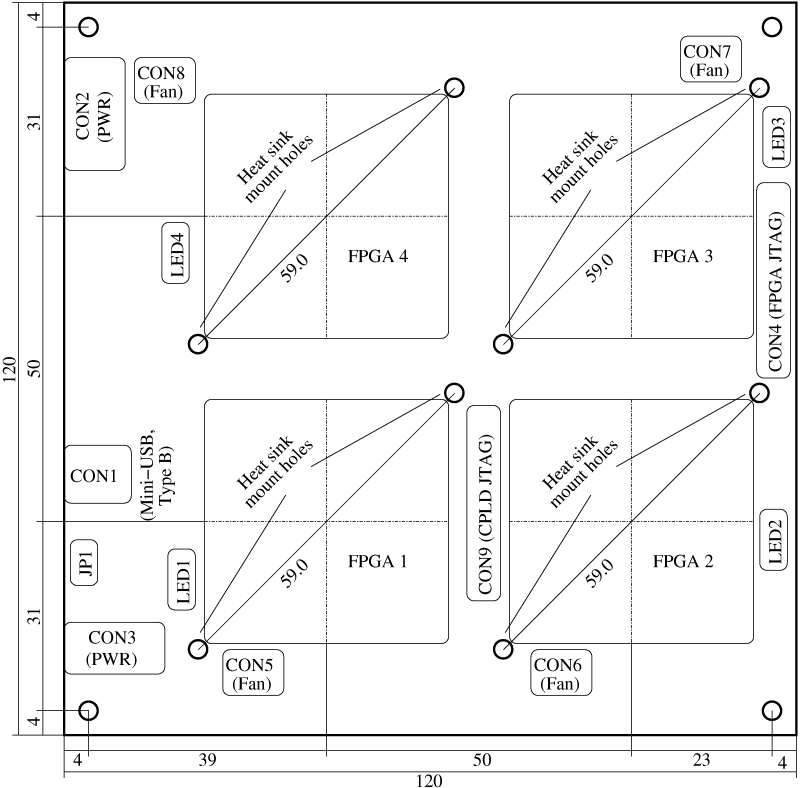

Die folgende Zeichnung zeigt die Maße sowie die Lage der beschriebenen Elemente.

Klicken sie auf das Bild für eine größere Version oder laden Sie die PDF-Version herunter.

FPGA-Konfiguration

Es gibt zwei Möglichkeiten das FPGA zu konfigurieren:- Vom USB. Das kann entweder mittels API (siehe configureFpga) oder mittels FWLoader oder dem DeviceServer erfolgen. Der DeviceServer ermöglicht den bequemem Zugriff auf das FPGA-Board mittels HTTP-Interface und Webbrowser als GUI.

- Via JTAG, siehe JTAG-Abschnitt unten. Das Hochladen des Bitstreams auf große FPGA's (wie XC6SLX150) via JTAG kann ziemlich lange dauern. Deshalb sollte die USB-Methode bevorzugt werden.

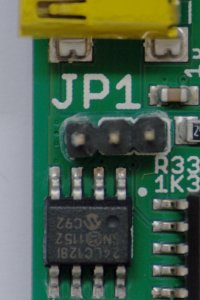

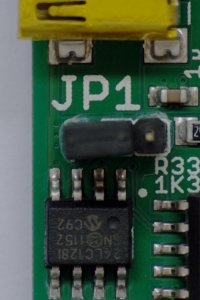

EEPROM-Adresse: JP1

Jumper JP1 legt die I2C-Adresse des EEPROM wie folgt fest:

| JP1 | I2C-Adresse |

| offen | 0xA2 |

| geschlossen | 0xAA |

Der EZ-USB FX2 Mikrocontroller sucht die Firmware an der Adresse 0xA2, welches die Standard-Adresse ist (Jumper offen).

Der Hauptzweck des Jumpers ist die Deaktivierung des EEPROM-Boot-Laders. Falls z.B. der EEPROM mit einer defekten Firmware programmiert wurde, kann der Mikrocontroller mit der internen Standard-Firmware gestartet werden, wenn JP1 während des Einschaltens geschlossen ist.

JP1 hat einen nicht verbundenen Pin der zum Parken des Jumpers genutzt werden kann. Die folgenden Bilder zeigen alle möglichen Jumper-Positionen:

|

|

| Rev. 1: JP1 offen | Rev. 1: JP1 geschlossen |

|

|

| Rev. 2: JP1 offen | Rev. 2: JP1 geschlossen |

FPGA-Status: LED1-LED4

LED1-LED4 zeigt den Konfigurations-Zustand des FPGA's wie folgt an:

| LED<n> | FPGA<n> |

| an | unkonfiguriert |

| aus | konfiguriert |

Externe Stromversorgung: CON2 und CON3

CON3 ist eine Standard-Gleichstrombuchse mit 2,1mm Innenstift (+) und 5,5mm Zylinder (-) für eine Versorgungsspannung von 4.5 V bis 16 V.CON2 ist eine steckbare Anschlussklemme. Die beiden äußeren Kontakte sing GND (-) und der innere Kontakt ist die Versorgungsspannung (+). Dieser Steckverbinder ist für hohe Ströme ausgelegt uns sollte deshalb bevorzugt werden. Der Anschluss-Block wird mitgeliefert.

Wenn unstabilisierte Stromversorgungen genutzt werden, muss sichergestellt sein, dass die Spitzen-Leerlaufspannung kleiner als 16V ist, siehe auch Leitfaden zur Auswahl der Stromversorgung auf der Wiki.

Vorschläge zur Stromversorgung von FPGA-Clustern befinden sich auf der FPGA-Cluster-Stromversorgungen Seite der Wiki.

Konfigurations-Beschleuniger- und Taktverteiler-CPLD

Das CPLD beschleunigt die FPGA-Konfiguration auf bis zu 24MB/s und verteilt die Takt-Signale. Ein Blockdiagramm welches die Funktion des CPLD veranschaulicht wird unten abgebildet.

Der schnelle Konfigurations-Modus benötigt einen Ausgangs-Endpoint des EZ-USB FX2. Die Firmware ermöglicht es, einen für benutzerdefinierte Kommunikation gedachten Endpoint (wieder-) zu verwenden. Wenn alle Endpoint-Puffer des EZ-USB FX2 für Eingangs-Endpoints benötigt werden, muss die FPGA-Konfiguration in normaler Geschwindigkeit (ca. 1 MByte/s) via Endpoint 0 erfolgen.

Das CPLD ist werksseitig programmiert. Eine Neu-Programmierung ist via CPLD-JTAG (CON9) möglich. Die Quell-Dateien und die jed-Datei können hier herunter geladen werden: usb-fpga-1.15y-cpld.zip.

FPGA-JTAG (CON4)

Das FPGA kann entweder über USB oder über JTAG konfiguriert werden. Wird das JTAG-Interface zum Konfigurieren des FPGA's verwendet, muss Bit 0-3 am Port E des EZ-USB FX2 Mikrocontrollers (=PROG_B an FPGA1-4) auf High gesetzt werden. Die geschieht automatisch wenn eine mit den SDK entwickelte Firmware geladen ist.

Der JTAG-Steckverbinder CON4 ist nicht standardmäßig installiert. Er wird auf Anfrage mitgeliefert.

Taktquellen

Auf dem FPGA-Board stehen zwei Taktquellen zur Verfügung: der Taktausgang des EZ-USB FX2, welcher normalerweise auf 48 MHz konfiguriert ist, und der Interface-Takt, welcher auf 30 MHz oder 48 MHz eingestellt werden kann. Aus diesen können mittels DCM's oder PLL's andere Takte im FPGA generiert werden.The Takt-Signale werden mittels des CPLD verteilt.

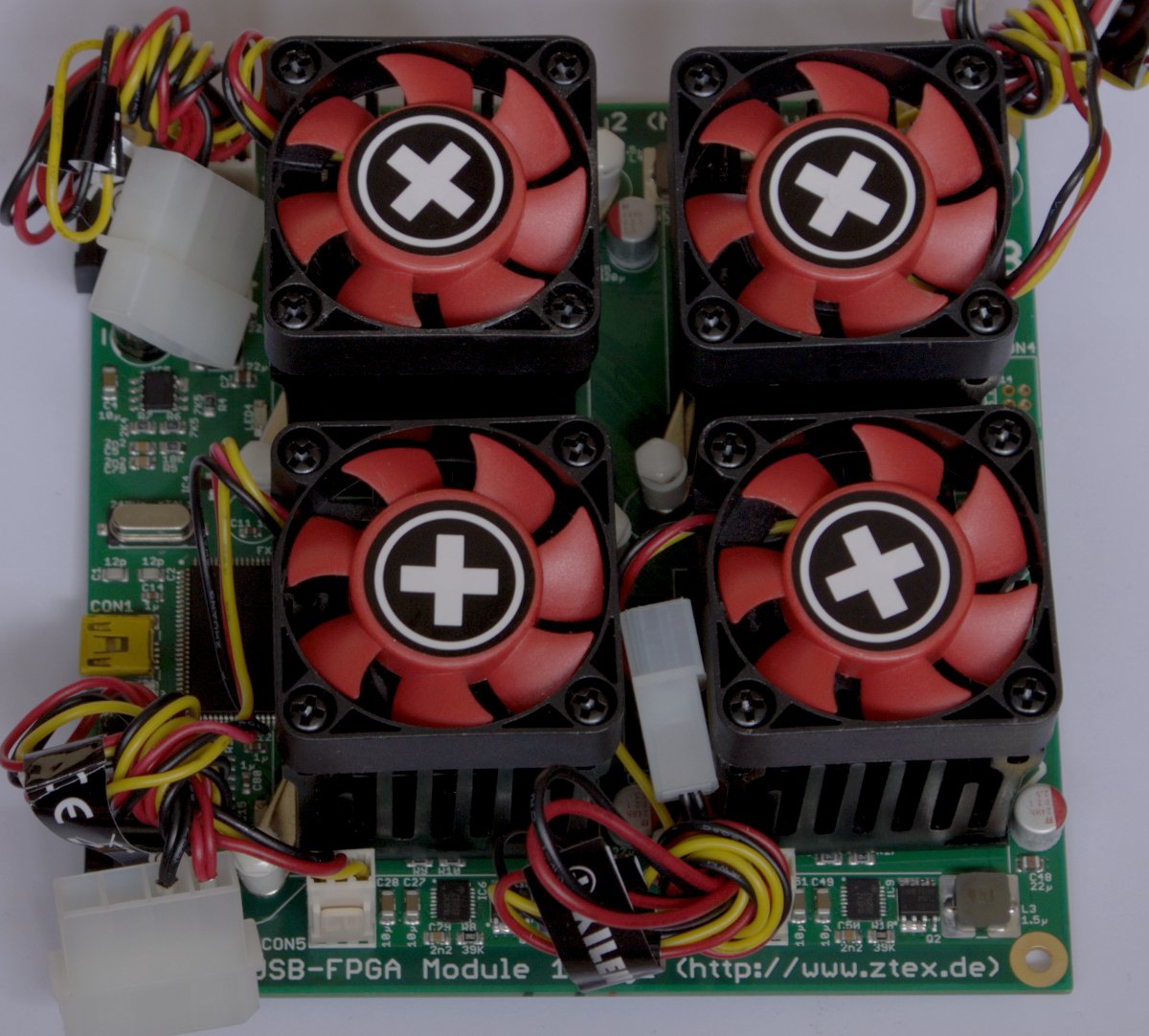

Kühlkörper

Für Hochgeschwindigkeits-Anwendungen werden Kühlkörper benötigt. USB-FPGA-Module 1.15y sind für große Standard-Kühlkörper (bis 40 mm x 40 mm) mit Push-Pins und einem Loch-Abstand von 59 mm ausgelegt. Wenn die Eingangs-Spannung 12V beträgt, können CON5-8 zum Anschluss von Lüftern verwendet werden.Vier Xilence COO-XPNB.F Kühlkörper gehören zum Lieferumfang. Dieser Kühlkörper kann aktiv und passiv genutzt werden. Bei passiver Nutzung sollte der Lüfter entfernt werden. Die Höhe des Kühlkörpers (ohne Lüfter) beträgt 35 mm. Die Höhe des Lüfters beträgt 11 mm.

Um eine ausreichend Wärmeübertragung sicher zu stellen, muss der Kühlkörper mittels Push-Pins und Wärmeleitpaste montiert werden.

Für eine Kühl-Lösung mit niedriger Bauweise werden Titan TTC-CSC03 Kühler empfohlen.

Liste der Verbindungen

Eine Liste der Verbindungen kann im Gnumeric- und Excel-Format heruntergeladen werden.

Bilder

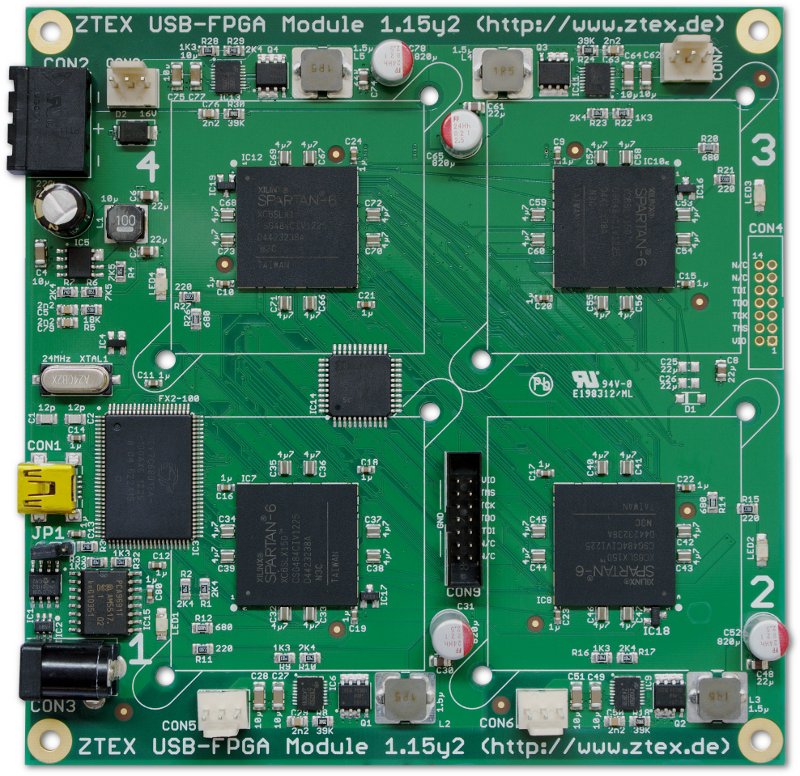

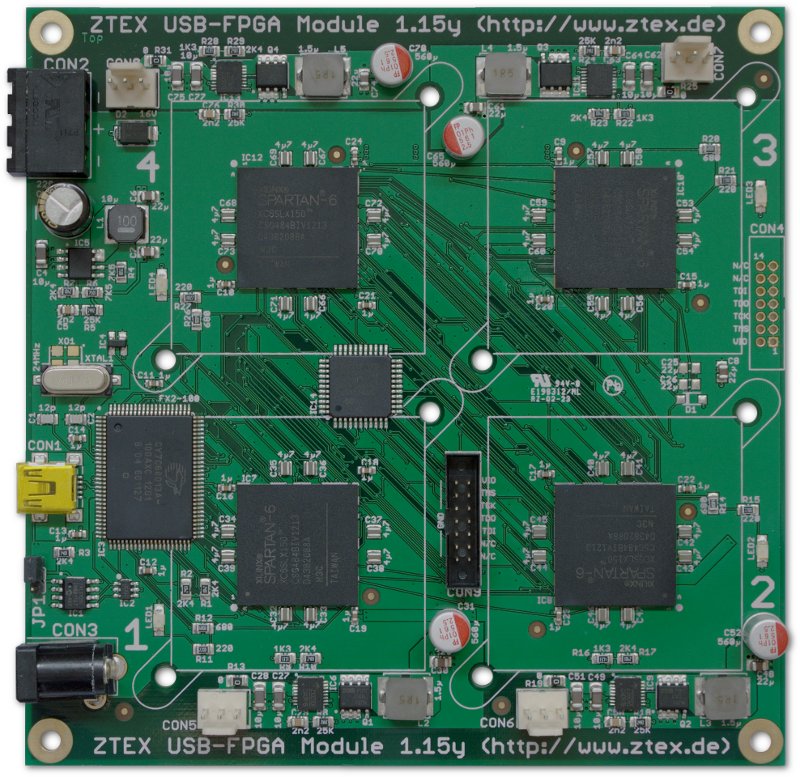

Klicken Sie auf die Bilder für vergrößerte Versionen.

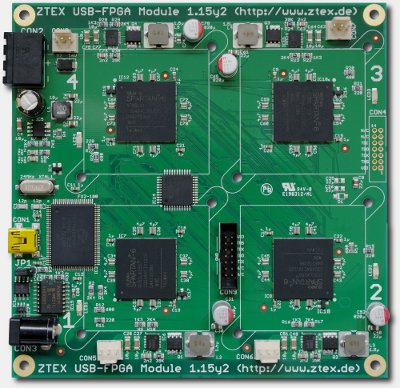

USB-FPGA-Modul 1.15y, Rev. 2 ohne Kühlkörper. Das Quad-Spartan 6 LX150 (XC6SLX150) FPGA-Board ist für kryptographische Berechnungen optimiert und ermöglicht den Bau von kostengünstigen FPGA-Clustern mittels Standard-Komponenten. |

USB-FPGA-Modul 1.15y, Rev. 1 ohne Kühlkörper. Das Quad-Spartan 6 LX150 (XC6SLX150) FPGA-Board ist für kryptographische Berechnungen optimiert und ermöglicht den Bau von kostengünstigen FPGA-Clustern mittels Standard-Komponenten. |

USB-FPGA-Modul 1.15y mit installiertem Kühlkörpers (gehört Lieferumfang). Dieses FPGA-Board besitzt vier Spartan 6 LX150 (XC6SLX150) FPGA und eignet sich vor Allem für kryptographische Berechnungen wie Bitcoin-Mining. |