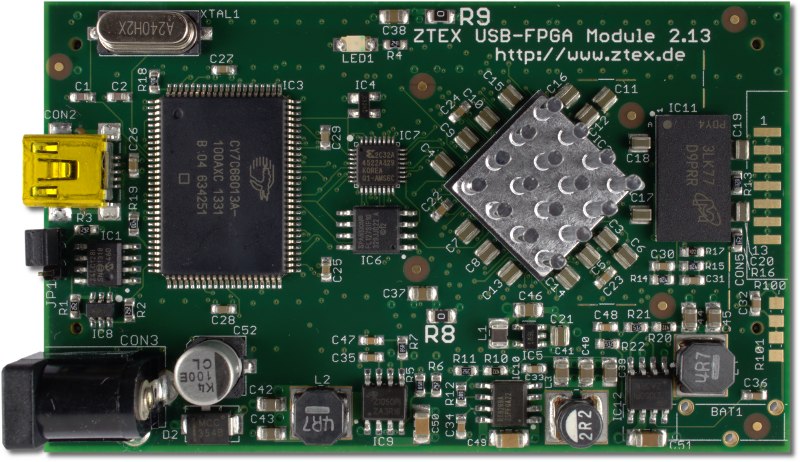

USB-FPGA-Modul 2.13:

Artix 7 FPGA-Board mit EZ-USB FX2 und DDR3 SDRAM

|

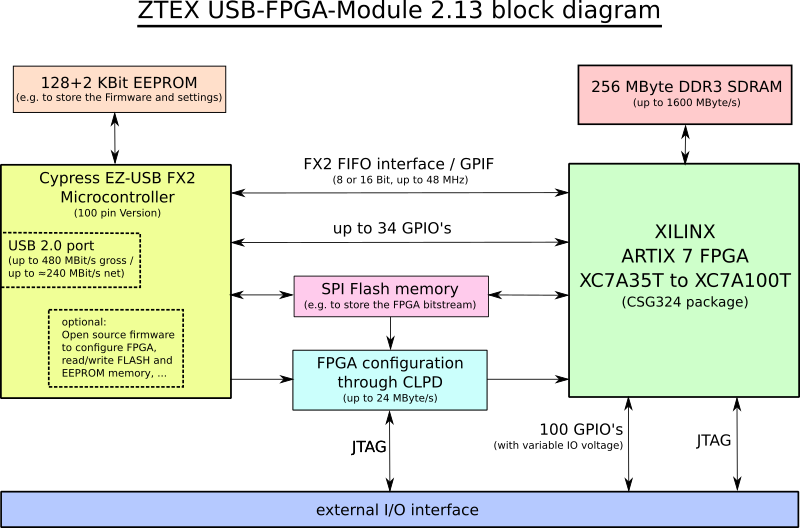

Blockdiagramm

Schaltplan |

|

Blockdiagramm

Eigenschaften

- USB 2.0-Schnittstelle mit Mini-USB-Buchse (Typ B)

- Cypress CY7C68013A EZ-USB FX2 Mikrocontroller (100 Pin Version)

- Vier Artix 7 Varianten: XC7A35T, XC7A50T, XC7A75T und XC7A100T, siehe Varianten

- Externer-I/O-Verbinder (bestehend aus zwei 2x32-Pin-Buchsenleisten mit 2.54mm-Raster) liefert:

- 100 mit dem FPGA verbundene General-Purpose-I/O's (GPIO's)

- JTAG-Signale

- Reset-Signal

- Externer Spannungseingang (4,5 V .. 16 V)

- 3,3V Ausgang

- I/O-Spannungs-Ausgang oder -Eingang, siehe Externer-I/O-Verbinder

- Gleiche Pin-Belegung wie USB-FPGA Modul 2.14 und USB-FPGA Modul 2.12

-

256 MByte DDR3 SDRAM:

- Bis zu 400 MHz Speichertakt

- 16 Bit Busbreite

- Datenrate bis zu 1600 MByte/s

- Mit dem Xilinx Memory Interface Generator (MIG) nutzbar, Beispiele befinden sich im SDK

- 128 MBit on-board Flash Speicher

- Ermöglicht das Laden des Bitstream vom FPGA (16.5 MByte/s)

- Zugreifbar vom EZ-USB FX2 und vom FPGA, siehe CPLD-Beschreibung

- 128 Kbit EEPROM-Speicher (kann zum Laden der Firmware genutzt werden)

- 2 Kbit MAC-EEPROM: enthält eindeutige, nicht löschbare MAC-Adresse und wird zum Speichern von Firmware-Einstellungen genutzt

- Schnelle FPGA configuration via USB mittels CPLD: bis zu 24MByte/s

- On-Board Stromversorgung:

- 3,3 V: 2000 mA

- 1,8 V: 1000 mA

- 1,5 V: 2000 mA

- 1,0 V: 4000 mA

- XC7A50T-, XC7A75T- und XC7A100T-Varianten: Kühlkörper für High-Performance- / Hochgeschwindigkeits-Anwendungen, siehe Abschnitt Kühlkörper

- Optional:

- Batterie zum Speichern eines Schlüssels für Bitstream-Verschlüsselung

- On-board JTAG-Steckverbinder

Varianten

Vier Varianten mit unterschiedlichen FPGA's werden angeboten:

| Variante | FPGA | Speedgrade (größer bedeutet schneller) |

Temperatur-Bereich | Status |

| USB-FPGA-Modul 2.13a | XC7A35T | 1C | 0-70°C | Wird ersetzt durch USB-FPGA Modul 2.12b. Restbestände im Shop |

| USB-FPGA-Modul 2.13b | XC7A50T | 1C | 0-70°C | Produktion läuft aus, Lagertyp, zum Shop |

| USB-FPGA-Modul 2.13b2 | XC7A50T | 1I | -40-85°C | In Produktion, Lagertyp, zum Shop |

| USB-FPGA-Modul 2.13c | XC7A75T | 2C | 0-70°C | In Produktion, Lagertyp, zum Shop Langzeitverfügbarkeit |

| USB-FPGA-Modul 2.13d | XC7A100T | 2C | 0-70°C | In Produktion, Lagertyp, zum Shop |

Alle Varianten werden von den kostenlosen Vivado-Webpack-Versionen unterstützt.

Funktions-Beschreibung

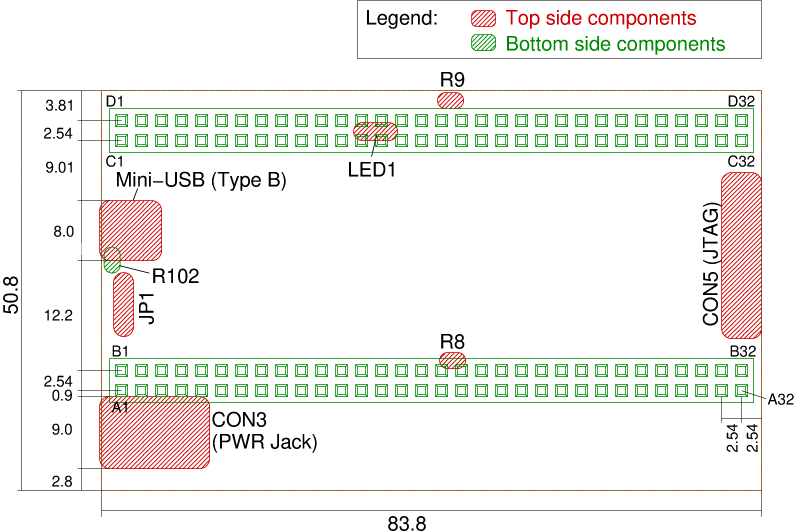

Die folgende Zeichnung zeigt die Maße sowie die Lage der beschriebenen Elemente.

Klicken sie auf das Bild für eine größere Version oder laden Sie die PDF-Version herunter.

USB-FPGA Module 2.13 haben keine Montage-Löcher da sie i.d.R. auf eine Anwendungs-Schaltung gesteckt werden. Alternativ dazu kann auch eine der Zusatzkarten als Montage-Adapter verwendet werden.

Gemeinsame Funktionen aller FPGA-Boards der Serie 2

USB-FPGA Module 2.13 sind FPGA-Boards der Serie 2. Funktionen, die alle FPGA-Boards dieser Serie besitzen, sind auf FPGA-Board-Serie 2 beschrieben.EEPROM-Adresse: JP1

Jumper JP1 legt die I2C-Adresse des EEPROM wie folgt fest:

| JP1 | I2C-Adresse |

| offen | 0xA2 |

| geschlossen | 0xAA |

JP1 wird verwendet um um zu verhindern, dass die Firmware aus dem EEPROM geladen wird. Der EZ-USB FX2 Mikrocontroller sucht die Firmware an der I2C-Adresse 0xA2 (JP1 offen) und bootet mit einer internen Firmware falls keine gültigen Daten an dieser Adresse gefunden werden (Jumper geschlossen).

JP1 hat einen nicht verbundenen Pin der zum Parken des Jumpers genutzt werden kann. Die folgenden Bilder zeigen alle möglichen Jumper-Positionen:

|

|

| JP1 offen | JP1 geschlossen |

FPGA-Status: LED1

LED1 zeigt den Konfigurations-Zustand des FPGA's wie folgt an:

| LED1 | FPGA |

| an | unkonfiguriert |

| aus | konfiguriert |

Stromversorgung, CON3

Die externe Stromversorgung kann über CON3 oder die Pins A1 and B1 des externen I/O-Verbinders erfolgen und sollte zwischen 4.5V V und 16 V liegen. CON3 ist eine Standard-Gleichstrombuchse mit 2,1mm Innenstift (+) und 5,5mm Zylinderdurchmesser (-). A1 und B1 des I/O-Verbinders und der Innenstift von CON3 sind direkt verbunden. Dadurch kann eine Basisplatine auch vom FPGA-Board versorgt werden.Für die meisten Anwendungen (insbesondere wenn der Speicher verwendet wird) garantiert der USB-Standard nicht genügend Strom um USB-FPGA Module 2.13 zu versorgen. Nichtsdestotrotz kann das FPGA-Board vom USB versorgt werden indem der optionale 0 Ω Widerstand R102 (Gehäuse 0805) installiert wird (Unterseite unter USB-Buchse, siehe Zeichnung). In diesem Fall muss sichergestellt sein, dass keine zweite Stromversorgung an CON3 oder die Pins A1 and B1 des externen I/O-Verbinders angeschlossen ist.

Taktquellen

Auf dem FPGA-Board sind zwei Taktquellen mit den FPGA verbunden: der Taktausgang des EZ-USB FX2, welcher normalerweise auf 48 MHz konfiguriert ist, und der Interface-Takt, welcher auf 30 MHz oder 48 MHz eingestellt werden kann. Aus diesen können mittels MMCM's oder PLL's andere Takte im FPGA generiert werden.Zusätzliche Taktsignale können an die MRCC and SRCC-Pins des I/O-Steckverbinders angeschlossen werden. (Diese Pins sind als differentielle Paare organisiert, z.B. L12P_T1_MRCC_35 und L12N_T1_MRCC_35. Single-ended Takte müssen an das positive Pin angeschlossen werden z.B. L12P_T1_MRCC_35.)

In den meisten Fällen sind die Onboard-Taktquellen ausreichend.

Konfigurations-Booster-CPLD und Flash-Speicher

Das CPLD ermöglicht die schnelle FPGA-Konfiguration via USB (bis zu 24 MByte/s). Dafür wird ein Ausgangs-Endpoint des EZ-USB FX2 benötigt. Die Firmware ermöglicht es, einen für benutzerdefinierte Kommunikation gedachten Endpoint (wieder-) zu verwenden. Wenn alle Endpoint-Puffer des EZ-USB FX2 für Eingangs-Endpoints benötigt werden, muss die FPGA-Konfiguration in normaler Geschwindigkeit (ca. 1 MByte/s) via Endpoint 0 erfolgen.Das CPLD kontrolliert auch den Zugriff auf den Flash-Speicher und die Konfiguration-Pins des FPGA's, welche von unterschiedliche Konfigurations-Quellen benötigt werden. Die folgende Tabelle gibt einen Überblick über die Zugriffs- und Konfigurations-Modi. Die Konfiguration-Modus-Pins CM1:CM0 des CPLD werden vom FX2 gesteuert. Sie besitzen einen internen Pull-Up-Widerstand sodass der Standard-Modus beim Starten des FX2 1:1 ist. M2:M1:M0 sind die Modus-Pins des FPGA welche vom werden vom CPLD gesteuert werden.

| CM1:CM0 | M2:M1:M0 | CCLK gesteuert von: | Konfigurations-quelle | Zugriff auf Flash-Speicher vom: |

| 1:1 | 1:0:1 | - | nur JTAG | FX2 |

| 1:0 | 1:1:0 | FX2:CTL5 | USB (High-Speed-Modus, bis 24 MByte/s) oder JTAG | - |

| 0:1 | 1:1:0 | FX2:PC6 | USB (Low-Speed-Modus, ca. 1 MByte/s) oder JTAG | - |

| 0:0 | 0:0:1 | FPGA | Flash (bis to 16.5 MByte/s) oder JTAG | FPGA (und FX2 nach erfolgreicher Konfiguration) |

Diese Tabelle ist nur eine kurze Zusammenfassung, da alle Konfigurations-Angelegenheiten automatisch von der Firmware und vom werksseitig programmierten CPLD gehandhabt werden. Interessierte Nutzer werden auf den Schaltplan und das CPLD-Datenpaket usb-fpga-2.13-2.16-cpld.zip verwiesen, welches die Quelldateien und die jed-Datei zum Programmieren des CPLD's via JTAG beinhaltet.

Weitere Information über die Verwendung des Flash-Speichers für die FPGA-Konfiguration befinden sich auf der ZTEX Wiki.

Externer I/O-Verbinder

Der externe I/O-Verbinder ist kompatibel zu anderen FPGA-Boards der Serie 2 und deshalb auf FPGA-Board-Serie 2 beschrieben. Die Pinbelegung ist die gleiche wie für USB-FPGA-Module 2.14. Dies erlaubt eine einfache Migration zwischen diesen beiden FPGA-Boards.Bei USB-FPGA-Modulen 2.13 sind alle 100 I/O's belegt und haben eine variable I/O-Spannung. Die I/O-Spannung ist VCCO_AB für die Reihen A und B und VCCO_CD für die Reihen C und D. Werksseitig sind VCCO_AB und VCCO_CD über die 0Ω Widerstände R8 bzw. R9 mit 3.3V verbunden. Somit sind diese Pins 3.3V Ausgänge. (Das ist das Standard-Verhalten aller FPGA-Boards der Serie 2). Wird eine andere I/O-Spannung benötigt, können R8 und/oder R9 ausgelötet werden und VCCO_AB bzw. VCCO_CD als Spannungs-Eingang verwendet werden.

Kühlkörper

Für einige Anwendungen könnte ein Kühlkörper benötigt werden. Die Varianten b bis d (XC7A50T, XC7A50T and XC7A100T) werden mit einem Kühlkörper-Kit geliefert welches aus folgenden Komponenten besteht:- 1 14×14×10mm passiver Kühlkörper

- 2 beidseitig klebende Wärmeleitpads

Der Kühlkörper können sicher entfernt werden, indem er mit einer dünnen Messerschneide der Kühlkörper an einer Ecke angehoben wird. Ausheben mit einem Schraubenzieher o.ä. kann zu einer Beschädigung der Leiterplatte führen.

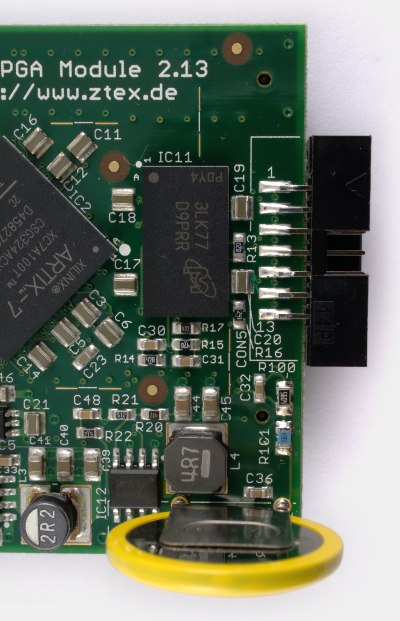

JTAGDas FPGA kann entweder über USB oder über JTAG konfiguriert werden. Die JTAG-Signale stehen auf dem externen I/O-Steckverbinder zur Verfügung, JTAG Steckverbinder auf den meisten Zusatzkarten. Optional kann auch eine 14 Pin-Steckverbinder an der Seite (CON5) installiert werden. (Werksseitig wird dieser aus Platzgründen weggelassen.) Der passende Steckverbinder ist im Shop erhältlich.Das JTAG-Interface kann auch zum Neu-Programmieren des CPLD genutzt werden. Batterie-OptionFalls Bitstream-Verschlüsselung benötigt wird, kann eine standardisierte 3V Lithium-Batterie mit einem Rastermaß von 10×3mm installiert werden. Desweiteren müssen zwei 0805 SMD-Widerstände eingelötet werden, R100: 5,6 MΩ und R101: 3,3 MΩ. Unter Berücksichtigung der Selbstentladung sollte die Lebensdauer der Batterie mindestens 10 Jahre betragen.Mit der Batterie kann das FPGA einen Schlüssel für die Bitstream-Entschlüsselung in einem speziellen Speicher halten. Dieser Schlüssel wird mittels JTAG geladen. Um Schaden zu vermeiden muss R100 vor dem Einlöten der Batterie installiert werden. Auch sollte darauf geachtet werden, dass die Batterie später nicht kurzgeschlossen werden kann, da durch den Spannungsabfall der Speicherinhalt verloren ginge. Das Bild auf der Seite zeigt ein USB-FPGA-Modul 2.13 mit installierter Batterie, R100 und R101 und JTAG-Steckverbinder CON5. FPGA-Boards mit werksseitig installierten Batterie-Komponenten und/oder JTAG ist auf Anfrage erhältlich. Eine Anleitung zur Bitstream-Verschlüsselung befindet sich auf der Wiki. |

|

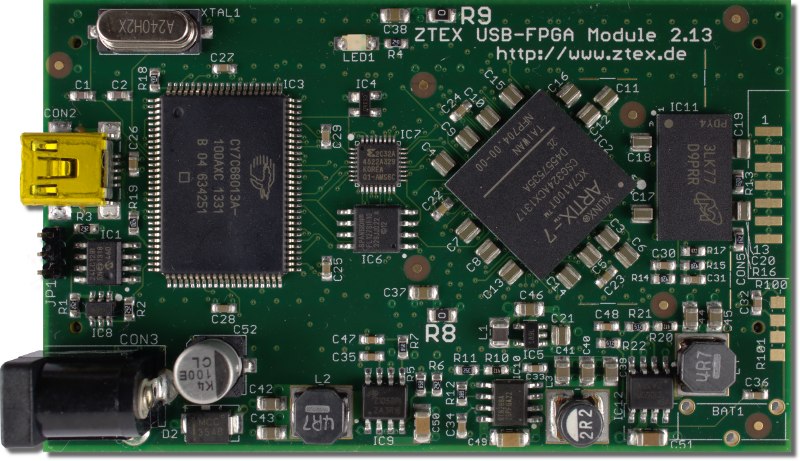

Bilder

Klicken Sie auf die Bilder für eine vergrößerte Darstellung.

Oberseite des USB-FPGA-Moduls 2.13d mit Artix 7 FPGA XC7A100T. |

Unterseite des USB-FPGA-Moduls 2.13. |

USB-FPGA-Modul 2.13d mit installiertem Kühlkörper. |