FPGA-Modul 2.00: FPGA-Board mit Spartan 6

|

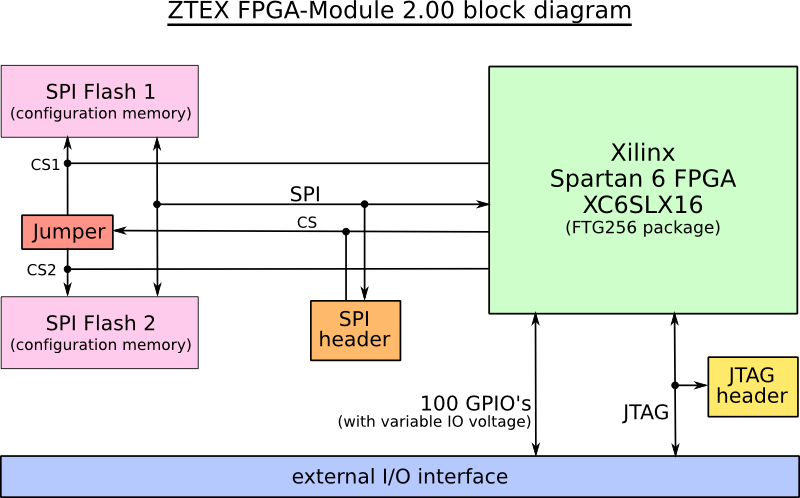

Blockdiagramm

Schaltplan |

|

Blockdiagramm

Eigenschaften

- Spartan 6 XC6SLX16 FPGA (XC6SLX9 und XC6SLX25 auf Anfrage)

- Externer-I/O-Verbinder (bestehend aus zwei 2x32-Pin-Buchsenleisten mit 2.54mm-Raster) liefert:

- 100 mit dem FPGA verbundene General-Purpose-I/O's (GPIO's)

- JTAG-Signale

- Reset-Signal

- Externer Spannungseingang (4,5 V .. 16 V)

- 3,3V Ausgang

- I/O-Spannungs-Ausgang oder -Eingang, siehe Externer-I/O-Verbinder

- Dual 16 MBit on-board Flash Speicher

- Ermöglicht das Laden des FPGA-Bitstreams (6.5 MByte/s)

- Chip durch Jumper wählbar

- On-Board Stromversorgung:

- Stromeingänge: USB-Buchse oder Externer-I/O-Verbinder

- 3,3 V: 2000 mA

- 1,2 V; 1000 mA

- Temperatur-Bereich: 0-70°C

Varianten

Drei Varianten mit unterschiedlichen FPGA's werden angeboten:

| Variante | FPGA | Speedgrade (größer bedeutet schneller) |

Verfügbarkeit |

| FPGA-Modul 2.00a | XC6SLX9 | 2 | Auf Anfrage (kein Lagertyp) |

| FPGA-Modul 2.00b | XC6SLX16 | 2 | Lagertyp, zum Shop |

| FPGA-Modul 2.00c | XC6SLX25 | 3 | Auf Anfrage (kein Lagertyp) |

All Varianten werden von den kostenlosen ISE-Webpack-Versionen unterstützt.

Beispiele und Vorlagen

FPGA-Module 2.00 werden nicht durch das ZTEX SDK unterstützt da sie keine PC-Schnittstelle (außer JTAG) besitzen. Stattdessen gibt es ein Beispiel-Paket welches auch Vorlagen für Pin-Definitionen enthält. Es ist im .tar.bz2- und .zip-Format verfügbar.Funktions-Beschreibung

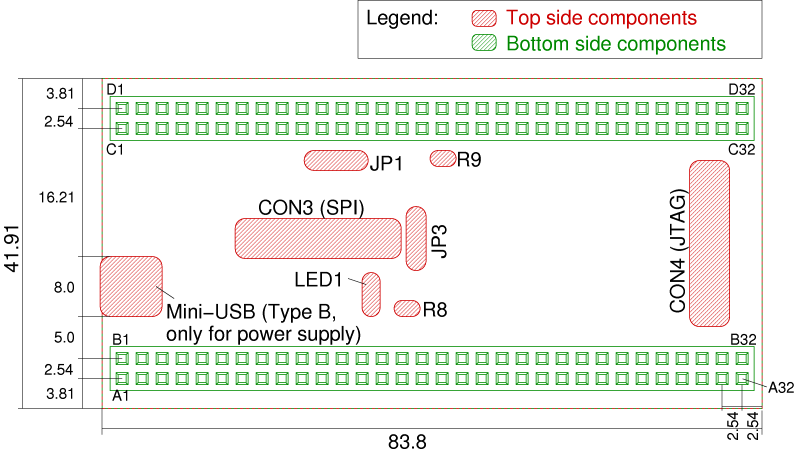

Die folgende Zeichnung zeigt die Maße sowie die Lage der im Folgenden beschriebenen Komponenten.

Klicken sie auf das Bild für eine größere Version oder laden Sie die PDF-Version herunter.

FPGA-Module 2.00 haben keine Montage-Löcher da sie i.d.R. auf eine Anwendungs-Schaltung gesteckt werden. Alternativ dazu kann auch eine der Zusatzkarten als Montage-Adapter verwendet werden.

FPGA-Konfiguration

Es gibt zwei Möglichkeiten das FPGA zu konfigurieren:- Via JTAG, siehe JTAG-Abschnitt unten.

- Vom Flash-Speicher, siehe Flash-Abschnitt unten.

Stromversorgung

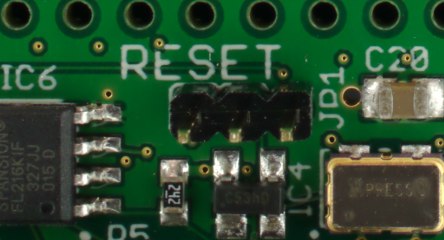

Die externe Stromversorgung kann über eine Mini-USB-Buchse (welche nur zur Stromversorgung genutzt werden kann) oder über die Pins A1 and B1 des externen I/O-Verbinders erfolgen. Die Versorgung über die USB-Buchse kann durch Auslöten des 0 Ω Widerstands deaktiviert werden. Dies kann sinnvoll sein, um Schaden durch versehentliches Anstecken eines USB-Kabels bei gleichzeitiger Stromversorgung über externen I/O-Verbinders zu verhindern.Reset, JP1

FPGA-Module 2.00 haben eine Reset-Schaltung. Der Reset kann wie folgt ausgelöst werden:- Pin D1 des externen I/O-Verbinders auf GND schalten

- Schließen von Jumper JP1

- Pin T4 des FPGA's auf GND schalten

Wichtig: Der Bitstream muss sicherstellen, dass Pin T4 des FPGA entweder offen ist oder hochgezogen wird, siehe Beispiele.

JP1 hat einen nicht verbundenen Pin der zum Parken des Jumpers genutzt werden kann. Die folgenden Bilder zeigen alle möglichen Jumper-Positionen:

|

JP1 offen |

|

JP1 geschlossen |

FPGA-Status: LED1

LED1 zeigt den Konfigurations-Zustand des FPGA's wie folgt an:

| LED1 | FPGA |

| an | unkonfiguriert |

| aus | konfiguriert |

Taktquellen

FPGA-Module 2.00 haben einen 26 MHz Oszillator welcher an Pin T7 des FPGA's angeschlossen ist. Aus diesem Takt können mittels DCM's oder PLL's andere Takte im FPGA generiert werden.Zusätzliche Taktsignale können an die GCLK-Pins des I/O-Steckverbinders angeschlossen werden.

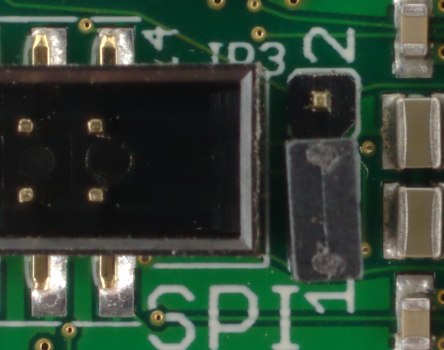

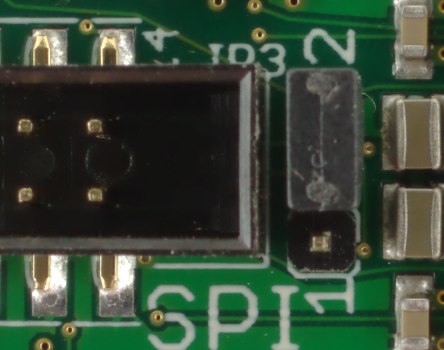

Flash-Speicher, JP3

FPGA-Module 2.00 besitzen zwei 16 MBit SPI Flash-Speicher. In der Regel dienen Sie zur Konfiguration des FPGA's.Beide Flash-IC's sind an einen gemeinsamen SPI-Bus angeschlossen, jedoch existieren drei Chip-Select (CS) Signale. CS1# ist mit Flash 1 (IC6) verbunden und CS2# mit Flash 2 (IC1), siehe Schaltplan. CS# wird über JP3 entweder auf Flash 1 oder auf Flash 2 geschaltet. Wird der Flash zur FPGA-Konfiguration verwendet, bestimmt somit JP3 dir Bitstream-Quelle:

|

Flash 1 ausgewählt |

|

Flash 2 ausgewählt |

Die maximale Konfigurations-Geschwindigkeit beträgt 6,5 MByte/s und wird bei einer SPI-Geschwindigkeit von 26MHz und SPI-Busbreite von 2 Bit erreicht (Bitgen-Einstellungen -g ConfigRate:26 -g SPI_buswidth:2). Der Bitstream kann indirekt via JTAG mittels der Xilinx-Tools geschrieben werden, siehe ZTEX Wiki, oder über den SPI-Sockel CON mit folgender Standard-Pinbelegung:

| Signal | Pins | Bemerkungen |

| MOSI | 10 | = Flash DIN |

| MISO | 8 | = Flash DOUT |

| SS | 4 | CS# signal, aktiviert Flash 1 oder 2 in Abhängigkeit von der Stellung von JP3 |

| SCK | 6 | = Flash CLK |

| WP | 14 | ON-Board Pullup-Widerstand |

| VIO | 2 | 3,3 V |

| GND | 1,3,5,7,9,11,13 |

Externer I/O-Verbinder

Der externe I/O-Verbinder ist kompatibel zu anderen FPGA-Boards der Serie 2 und deshalb auf FPGA-Board-Serie 2 beschrieben.Bei FPGA-Modulen 2.00 sind alle 100 I/O's belegt und haben eine variable I/O-Spannung. Die I/O-Spannung ist VCCO_AB für die Reihen A und B und VCCO_CD für die Reihen C und D. Werksseitig sind VCCO_AB und VCCO_CD über die 0Ω Widerstände R8 bzw. R9 mit 3.3V verbunden. Somit sind diese Pins 3.3V Ausgänge. (Das ist das Standard-Verhalten aller FPGA-Boards der Serie 2). Wird eine andere I/O-Spannung benötigt, können R8 und/oder R9 ausgelötet werden und VCCO_AB bzw. VCCO_CD als Spannungs-Eingang verwendet werden.

FPGA-Module 2.00 haben durchsteckbare Buchsenleisten, welche den beidseitigen Anschluss von Anwendungsschaltungen ermöglichen. Soll die Nutzer-Leiterplatte auf die Oberseite des FPGA-Boards gesteckt werden, müssen spezielle lange Stiftleisten verwendet werden. (Mit den im Shop erhältlichen Stiftleisten können Leiterplatten nur auf die Unterseite gesteckt werden.)

Die Pin-Belegung von FPGA-Moduls 2.00 und USB-FPGA-Modulen 2.01 ist gleich.

JTAG

Die JTAG-Signale stehen auf einem On-Board JTAG-Sockel CON4 und dem dem externen I/O-Steckverbinder zur Verfügung. CON4 hat Standard-Pinbelegung:

| Signal | Pins | Bemerkungen |

| TDI | 10 | |

| TDO | 8 | |

| TMS | 4 | |

| TCK | 6 | |

| VIO | 2 | 3.3 V |

| GND | 1,3,5,7,9,11,13 |

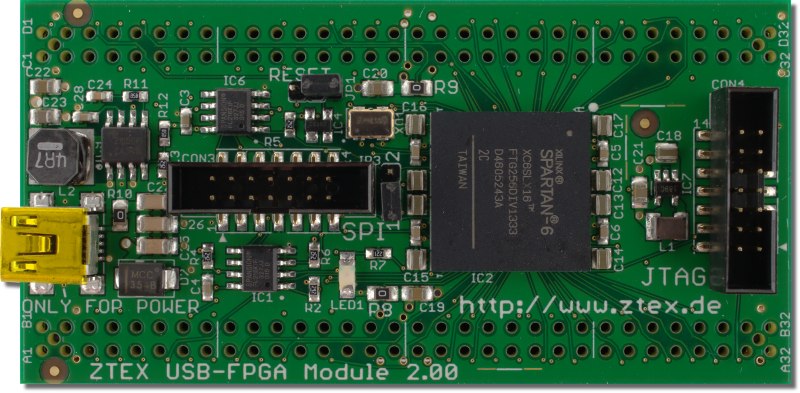

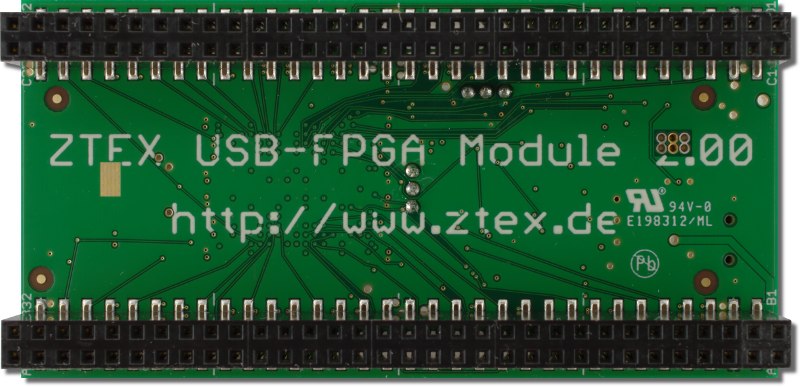

Bilder

Klicken Sie auf die Bilder für eine vergrößerte Darstellung.

Oberseite des FPGA-Moduls 2.00b mit Spartan 6 XC6SLX16 FPGA. |

Unterseite des FPGA-Moduls 2.00b. |