USB-FPGA Module 1.15x:

Spartan 6 LX150 FPGA Board with USB 2.0 Microcontroller

USB-FPGA Modules 1.15x are deprecated. Please switch to Series 2 FPGA Boards.

The old product page is still available here for documentation purposes.

|

The USB-FPGA Module 1.15x is a special variant of the USB-FPGA Module 1.15. It contains an on-board power supply and is optimized for computations that do not require much bandwidth and RAM. The FPGA Board can be used for building large low-cost clusters using standard components.

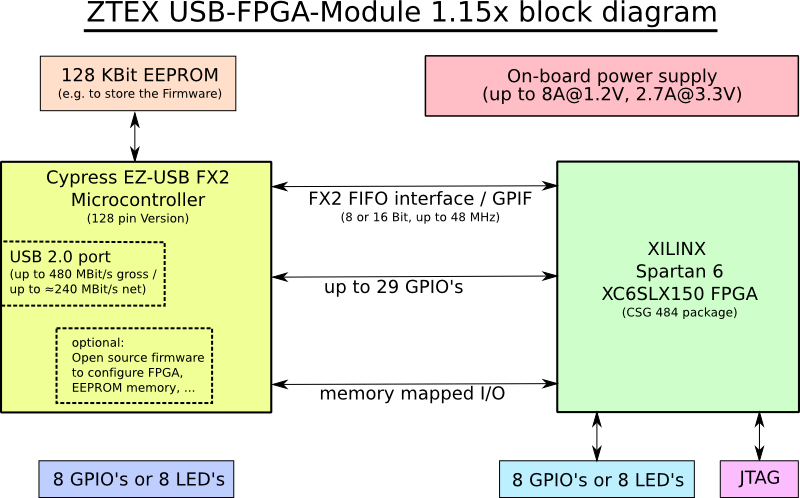

Block diagram

Schematics (PDF) |

|

Block diagram

Features

- Xilinx Spartan 6 FPGA LX150 (XC6SLX150) FPGA, speed grade 3 or 3N

- High-Speed (480 MBit/s) USB interface via Mini-USB connector (B-type)

- Cypress CY7C68013A EZ-USB FX2 Microcontroller

- Memory mapped IO between EZ-USB FX2 and FPGA

- 128 Kbit EEPROM memory (can be used to store the EZ-USB firmware)

- 2 Kbit MAC-EEPROM: contains a unique non erasable MAC-address

- High efficiency on-board power supply:

- Wide input range: 4.5 V to 16 V

- 3.3 V @ 2.5 A

- 1.2 V @ 8A

- Large heat sink for active or passive cooling

- 8 GPIO's from EZ-USB FX2 and 8 GPIO's from FPGA, can also be used for LED's

- FPGA configuration / programming via USB using the free SDK. (No JTAG adapters or other additional utilities required.)

- Non-free Xilinx ISE License or an Evaluation License required for FPGA development

Comparison with USB-FPGA Module 1.15d

- Firmware compatible, i.e. FPGA boards can be used with the same firmware and Bitstream

- On-board power supply

- Only a few GPIO's, mainly intended for debugging

- No SDRAM

- No microSD and no Flash memory

- No CPLD for fast configuration. Uploading an uncompressed Bitstream takes about 7s

- Larger heat sink

- All other features are the same

Applications

The FPGA Board is optimized for computations that do not require a much bandwidth and RAM such as:- Bitcoin-Mining

- Monte Carlo methods

- Computation of Rainbow Tables

- Brute-force searches

- Bioinformatic calculations

SDK, Examples, Getting Started

A powerful open source Firmware Development Kit with platform independent host software API is available for the FPGA Board. This SDK allows to define all USB device descriptors using only a few macro commands, and thus gives the developer a quick start into Firmware programming.The SDK package contains a lot of examples which can be used as starting point for own applications.

More Information are available in the EZ-USB FX2 SDK section.

Additional documentation including Tutorials can also be found on the ZTEX Wiki

Functional description

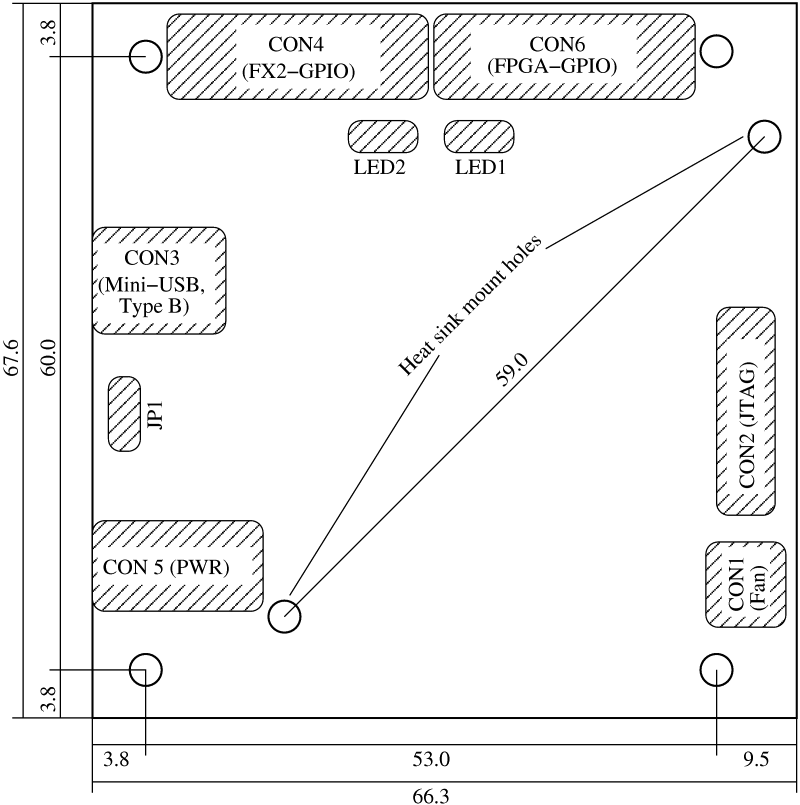

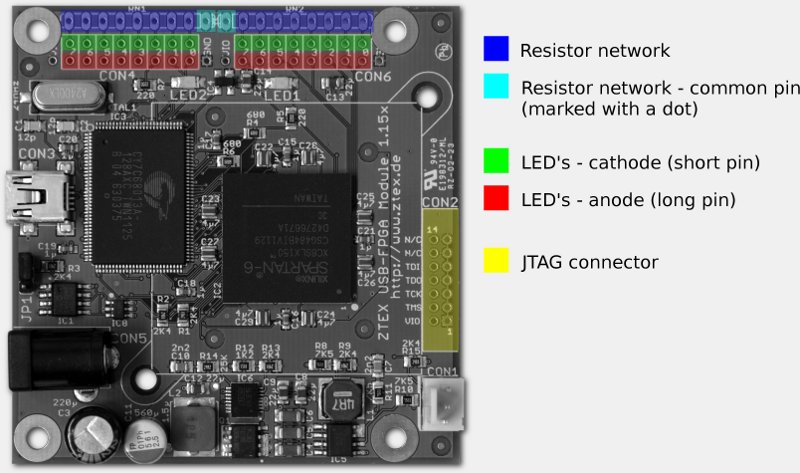

The following drawing shows the measurements and the location of the of the described elements.

Click on the image for a larger version or download the PDF version.

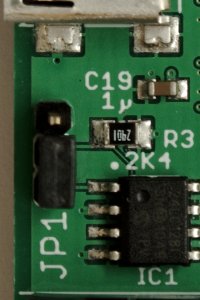

EEPROM address: JP1

Jumper JP1 specifies the I2C address of the EEPROM:

| JP1 | I2C address |

| open | 0xA2 |

| close | 0xAA |

The EZ-USB FX2 Microcontroller searches for the firmware at the address 0xA2 which is the default address (jumper open).

The main purpose of this jumper is to disable EEPROM boot-loading. If, for example, the EEPROM was programmed with a corrupt firmware the Microcontroller can be booted with the internal firmware by closing JP1 during powering-on the FPGA Board.

JP1 has an unconnected pin which can be used for parking the jumper. The following pictures show all possible jumper positions:

|

|

| JP1 open | JP1 closed |

FPGA state: LED1

LED1 indicates the configuration state of the FPGA as follows:

| LED1 | FPGA |

| on | unconfigured |

| off | configured |

LED2

LED2 is a general purpose LED and is connected to pin 0 of port A of the EZ-USB FX2.External power: CON5

CON5 is a standard DC power jack with 2.1mm center pin (+) diameter and 5.5mm barrel (-) diameter for a supply voltage of 4.5 V to 16 V. If non-stabilized power supplies are used it must be made sure that the peak voltage is not larger then 18V, see also Power supply selection guide on the Wiki.Two suggestions for the power supply of FPGA clusters are on the FPGA cluster power supplies page on the Wiki.

GPIO connectors or LED's

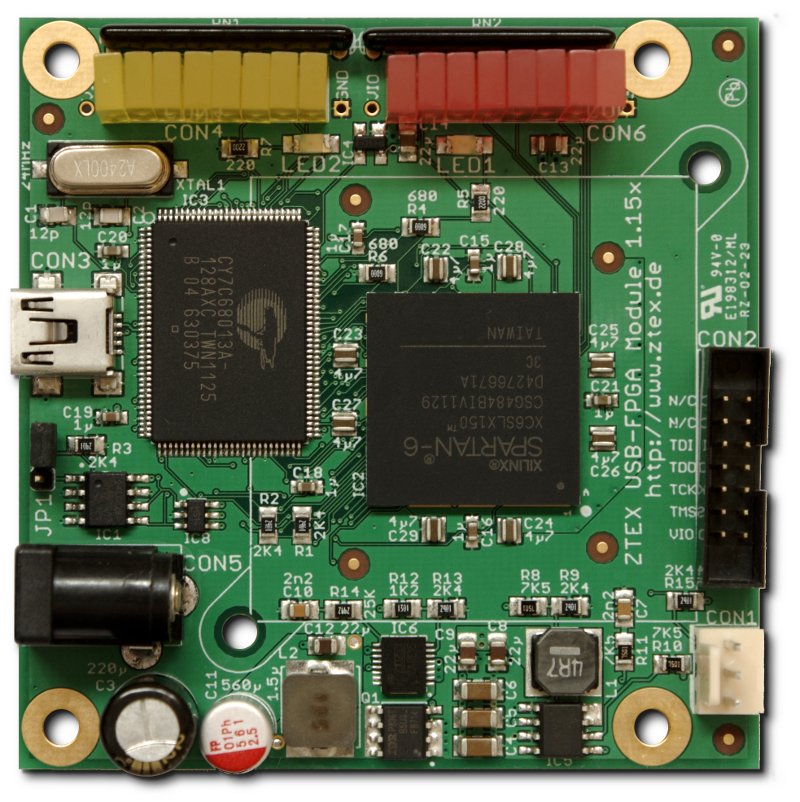

There are two 10 pin GPIO connectors on the FPGA board. Each one delivers 8 GPIO signals, one GND pin and one 3.3V (=VIO) pin. CON4 is connected the port E of the EZ-USB FX2 and CON6 is connected to the FPGA, see the schematics or List of Connections for details.Alternatively LED's can be installed on the GPIO connectors, see images below. These LED's may be very helpful for debugging during the development process. A Debug Kit with all necessary parts is available. The following picture shows an installation plan of the parts (also see images for a FPGA board with installed LED's):

JTAG

The FPGA can be configured either via USB or via JTAG. If the JTAG interface is used for FPGA configuration bit 1 of port A (=PROG_B at FPGA) must be driven high. This happens automatically if a firmware developed with the SDK is running.

The JTAG connector is not installed by default. It is a part of the Debug Kit.

Clock resources

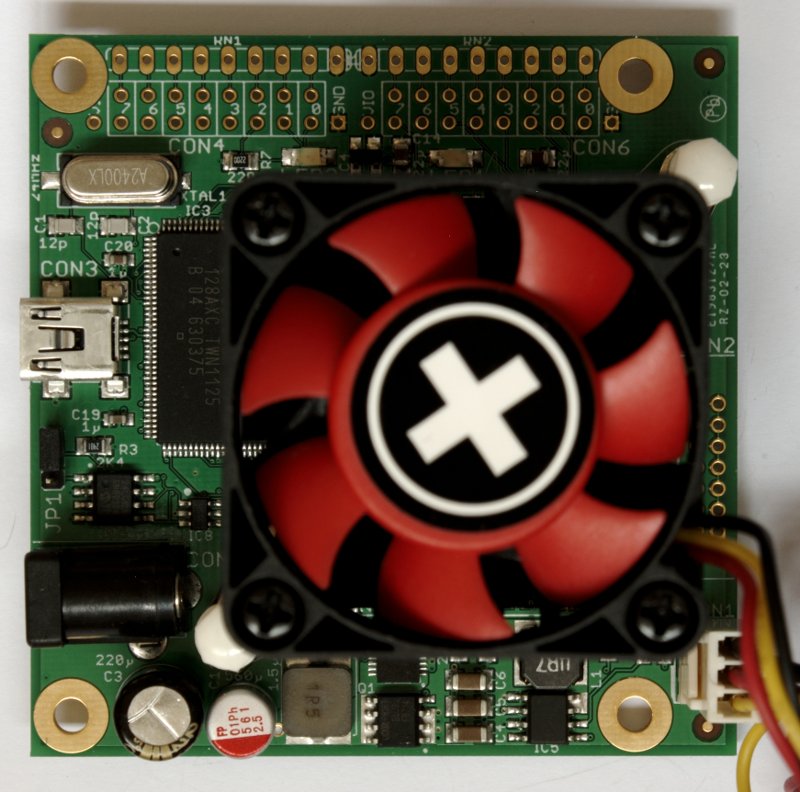

On the FPGA board two clocks sources are connected to the FPGA: the clock output of the EZ-USB FX2 which is usually configured to 48 MHz and the interface clock which can be configured to 30 MHz or to 48 MHz. They can be used to generate new clocks within the FPGA using DCM's or PLL's.Heat Sink

For high performance / high speed applications a heat sink is required. USB-FPGA Modules 1.15x are prepared for large standard heat sinks (up to 40 mm x 40 mm) with push pins and a hole distance of 59mm. If the input voltage is 12V CON1 can be used to connect a fan.A Xilence COO-XPNB.F heat sink is delivered with the board. This heat sink can be used actively or passively. In passive mode the fan should be removed. The height of the heat sink (without fan) is 35 mm. The height of the fan is 11 mm.

In order to ensure sufficient heat transfer the heat sink has to be mounted using the push pins and thermal grease.

If a low profile cooling solution is required the Titan TTC-CSC03 cooler is recommended.

List of Connections

A List of Connections can be downloaded in Gnumeric and Excel format.

Images

Click on the images for larger versions.

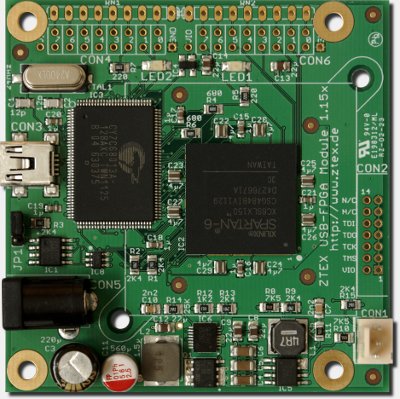

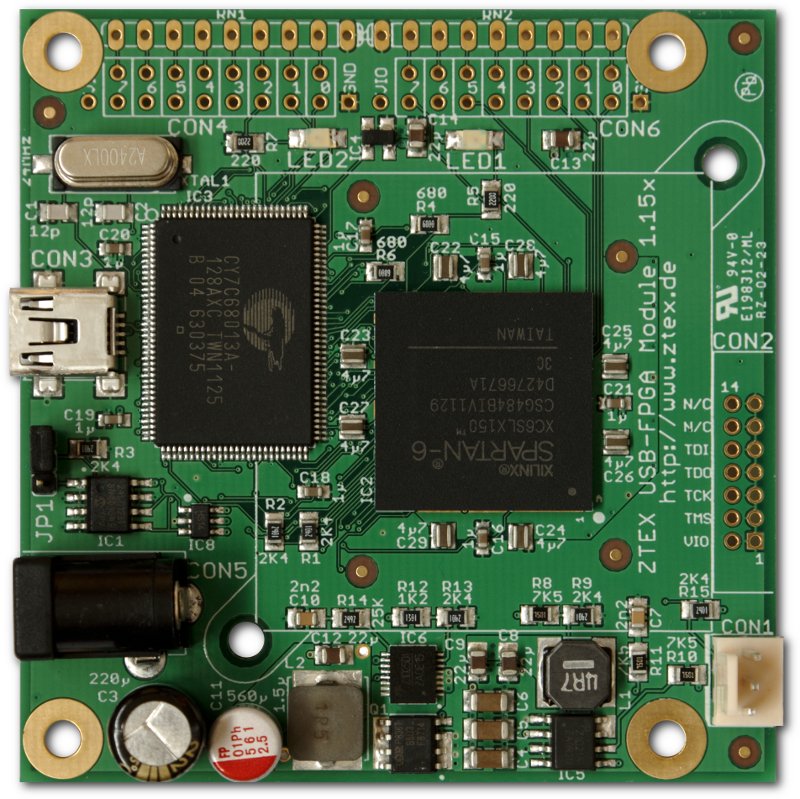

USB-FPGA Module 1.15x without heat sink. This Spartan 6 LX150 (XC6SLX150) FPGA Board is optimized for cryptographic computations and allows to build low-cost clusters using standard components. |

USB-FPGA Module 1.15x with installed heat sink. The heat sink is delivered with the board. This FPGA Board contains a Spartan 6 LX150 (XC6SLX150) FPGA and is suitable for cryptographic computations such as Bitcoin Mining. |

USB-FPGA Module 1.15x with installed Debug Kit. |