USB FPGA-Module-1.11:

Spartan 6 LX9 bis LX25 FPGA-Board mit USB 2.0-Mikrocontroller und 64 MByte DDR SDRAM

USB-FPGA-Module 1.11 sind veraltet. Bitte wechseln Sie zu FPGA Boards der Serie 2.

Als Übergangslösung ist ein Adapter verfügbar.

Die alte Produktseite ist hier weiterhin zu Dokumentationszwecken verfügbar.

|

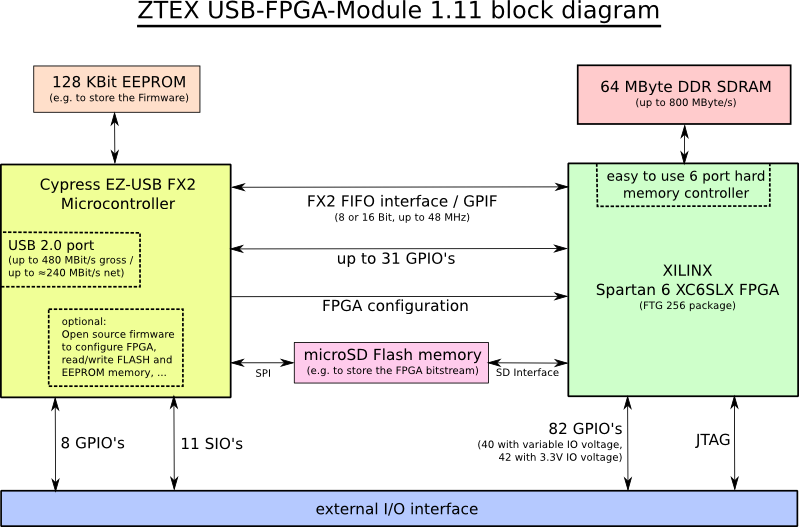

Blockdiagramm

Schaltplan (PDF) |

|

Blockdiagramm

Eigenschaften

- High-Speed (480 MBit/s) USB-Interface via Mini-USB-Buchse (Typ B)

- Cypress CY7C68013A EZ-USB FX2 Mikrocontroller

- Xilinx Spartan 6 LX9 bis LX25 FPGA (XC6SLX9 bis XC6SLX25), siehe Varianten

-

90 General Purpose I/O's (GPIO):

- 82 FPGA GPIO's

- 8 EZ-USB FX2 GPIO's

-

15 spezial-I/O's (SIO):

- 4 Pins für die FPGA-Konfiguration via JTAG

- 2 Pins für serielle Schnittstellen

- 2 Pins I2C-Interface

- 2 Interrupt-Pins

- 3 Timer

- 1 Wakeup-Pin

- 1 Breakpoint-Pin

-

64 MByte DDR SDRAM:

- 200 MHz Taktfrequenz

- 16 Bit Busbreite

- Bis zu 800 MByte/s Datenrate

- Einfach zu nutzender Hardware-Speichercontroller mit 6 Ports integriert im Spartan 6 FPGA. (siehe SDK für Beispiele)

- MicroSD-Sockel für microSD-Karten mit normaler und hoher Kapazität (SDHC) (Karten müssen SPI-Modus unterstützen)

- 128 Kbit EEPROM-Speicher (kann zum Laden der Firmware genutzt werden)

- Externe Stromversorgung erforderlich:

- 3,3 V; Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: ≥ 500 mA

- 2,5 V - 2,6 V: Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: ≥ 900 mA

- 1,2 V; Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: XC6SLX9: ≥ 500 mA, XC6SLX16: ≥ 750 mA, XC6SLX25: ≥ 1000 mA

- Variable I/O-Spannung VCCO_IO: 1,14...3,46 V; Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: ≥ 500 mA

- Temperatur-Bereich: 0-70°C (-25°C - 85°C auf Anfrage)

- FPGA-Konfiguration / -Programmierung via USB mittels des EZ-USB FX2 SDK. (Keine JTAG-Adapter oder andere zusätzliche Hilfsmittel erforderlich.)

- FPGA-Konfiguration / -Programmierung vom Flash-Speicher

Varianten

Es werden Varianten mit unterschiedlicher Ausstattung angeboten.

| Variante | FPGA | Speedgrade (größer bedeutet schneller) |

Buchsenleisten auf der Unterseite (zwei mal 2x32 und zwei mal 1x16) |

Verfügbarkeit |

| USB-FPGA-Modul 1.11a | XC6SLX9 | 2 | ja | Ausverkauft, wechseln Sie zu FPGA Boards der Serie 2 |

| USB-FPGA-Modul 1.11b | XC6SLX16 | 2 | nein | |

| USB-FPGA-Modul 1.11c | XC6SLX25 | 3 | ja |

SDK, Beispiele, Tutorials

Für das USB-FPGA-Board steht ein quelloffenes Firmware-Entwicklungskit mit plattform-unabhängiger Hostsoftware API zur Verfügung. Dieses SDK erlaubt die Festlegung der USB-Geräte-Deskriptoren mit nur wenigen Makro-Kommandos und ermöglicht so dem Entwickler einen schnellen Einstieg in die Firmware Programmierung.Das SDK-Paket enthält eine Vielzahl von Beispielen welche als Ausgangspunkt für eigene Entwicklungen genutzt werden können.

Für mehr Informationen wird auf Abschnitt EZ-USB FX2 SDK verwiesen.

Weitere Dokumentationen einschließlich Tutorials befinden sich auf der ZTEX Wiki.

Funktions-Beschreibung

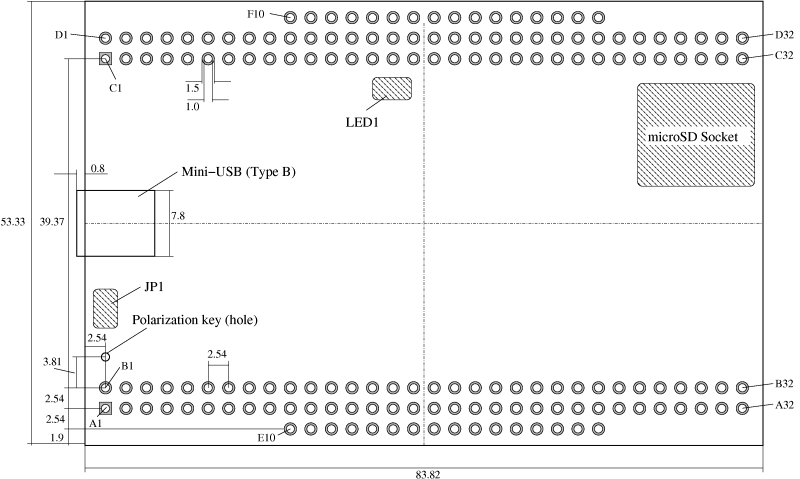

Die folgende Zeichnung zeigt die Maße sowie die Lage der beschriebenen Elemente.

Klicken sie auf das Bild für eine größere Version oder laden Sie die PDF-Version herunter.

FPGA-Konfiguration

Es gibt drei Möglichkeiten das FPGA zu konfigurieren:- Vom USB. Das kann entweder mittels API (siehe configureFpga) oder mittels FWLoader oder dem DeviceServer erfolgen. Der DeviceServer ermöglicht den bequemem Zugriff auf das FPGA-Board mittels HTTP-Interface und Webbrowser als GUI.

- Via JTAG, siehe JTAG-Abschnitt unten. Das Hochladen des Bitstreams via JTAG ist langsam. Deshalb sollte die USB-Methode bevorzugt werden.

- Vom microSD-Speicher, siehe Standalone-Beschreibung auf der ZTEX Wiki.

EEPROM-Adresse: JP1

Jumper JP1 legt die I2C-Adresse des EEPROM wie folgt fest:

| JP1 | I2C-Adresse |

| offen | 0xA2 |

| geschlossen | 0xAA |

Der EZ-USB FX2 Mikrocontroller sucht die Firmware an der Adresse 0xA2, welches die Standard-Adresse ist (Jumper offen).

Der Hauptzweck des Jumpers ist die Deaktivierung des EEPROM-Boot-Laders. Falls z.B. der EEPROM mit einer defekten Firmware programmiert wurde, kann der Mikrocontroller mit der internen Standard-Firmware gestartet werden, wenn die Pads des Jumpers JP1 während des Einschaltens kurzgeschlossen sind.

FPGA-Status: LED1

LED1 zeigt den Konfigurations-Zustand des FPGA's wie folgt an:

| LED1 | FPGA |

| an | unkonfiguriert |

| aus | konfiguriert |

Taktquellen

Auf dem FPGA-Board sind zwei Taktquellen mit den FPGA verbunden: der Taktausgang des EZ-USB FX2 welcher normalerweise auf 48 MHz konfiguriert ist, und der Interface-Takt, welcher auf 30 MHz oder 48 MHz eingestellt werden kann. Aus diesen können mittels DCM's oder PLL's andere Takte im FPGA generiert werden.Zusätzliche Taktsignale können an die GCLK-Pins des I/O-Steckverbinders angeschlossen werden.

In den meisten Fällen sind die Onboard-Taktquellen ausreichend.

I/O-Verbinder

Zwei 2x32-Pin und zwei 1x16-Pin Steckverbinder mit 2,54mm-Raster liefern die I/O-Signale und werden für die Stromversorgung genutzt. Die Zeichnung zeigt die Position der Verbinder.

Der I/O-Verbinder der Spartan 6 USB-FPGA-Module 1.11 ist mechanisch abwärtskompatibel zum I/IO-Verbinder der USB-FPGA-Module 1.2

In der Nähe des B1-Pins befindet sich eine Polarisierungs-Markierung in Form eines kleinen Loches, siehe Zeichnung. Um Beschädigung zu vermeiden muss die Polarisierungs-Markierung (Loch) aller miteinander verbundenen Boards gleich ausgerichtet sein.

JTAG

Das FPGA kann entweder über USB oder über JTAG konfiguriert werden. Die JTAG-Signale stehen an den Pins D29 bis D32 des I/O-Steckverbinders zur Verfügung. Beim Experimentier-Board und dem Stromversorgungs-Modul werden die JTAG-Signale auf einen 8-Pin oder 14 Pin-Steckverbinder geführt.

Wird das JTAG-Interface zum Konfigurieren des FPGA's verwendet, muss Bit 1 am Port A des EZ-USB FX2 Mikrocontrollers (=PROG_B am FPGA) auf High gesetzt werden. Die geschieht automatisch wenn eine mit den SDK entwickelte Firmware geladen ist.

Pinliste and Liste der Verbindungen

Die Pinliste des I/O-Verbinders und die Liste der Verbindungen können im Gnumeric- oder Excel-Format heruntergeladen werden. Diese Dateien beinhalten die Daten für alle USB-FPGA Boards einschließlich Kompatibilitätsinformationen. (Achtung: Die Dateien enthalten mehrere Blätter.)

Es folgt die Pinliste des I/O-Verbinders:

Pinliste

E

A

B

C

D

F

1

4..35V

4..35V

USB_5V

USB_5V

1

2

GND

GND

5V (unbenutzt)

5V (unbenutzt)

2

3

INT4

T0

R16~IO_L49N_M1DQ11_1

5V (unbenutzt)

3

4

T1

T2

GND

GND

4

5

BKPT

GND

INT5#

WAKEUP*

5

6

SCL

SDA

3,3V

3,3V

6

7

3,3V

3,3V

7

8

TxD0

RxD0

GND

K16~IO_L44N_A2_M1DQ7_1

8

9

B15~IO_L29P_A23_M1A13_1

B16~IO_L29N_A22_M1A14_1

PE7/GPIFADR8

L16~IO_L47N_LDC_M1DQ1_1

9

10

2,5V

2,5V

PE6/T2EX

M16~IO_L46N_FOE_B_M1DQ3_1

N16~IO_L45N_A0_M1LDQSN_1

10

11

1,2V

1,2V

PE5/INT6

P16~IO_L48N_M1DQ9_1

M15~IO_L46P_FCS_B_M1DQ2_1

11

12

A14~IO_L65N_SCP2_0

B14~IO_L65P_SCP3_0

PE4/RXD1OUT

P15~IO_L48P_HDC_M1DQ8_1

R15~IO_L49P_M1DQ10_1

12

13

A13~IO_L63N_SCP6_0

C13~IO_L63P_SCP7_0

GND

PE3/RXD0OUT

T15~IO_L50N_M1UDQSN_1

L14~IO_L47P_FWE_B_M1DQ0_1

13

14

C11~IO_L39P_0

D12~IO_L66N_SCP0_0

D11~IO_L66P_SCP1_0

PE2/T2OUT

K15~IO_L44P_A3_M1DQ6_1

N14~IO_L45P_A1_M1LDQS_1

14

15

A11~IO_L39N_0

E11~IO_L64N_SCP4_0

F10~IO_L64P_SCP5_0

PE1/T1OUT

R14~IO_L50P_M1UDQS_1

L13~IO_L53N_VREF_1

15

16

B10~IO_L35P_GCLK17_0

3,3V

3,3V

PE0/T0OUT

M13~IO_L74P_AWAKE_1

L12~IO_L53P_1

16

17

A10~IO_L35N_GCLK16_0

C10~IO_L37N_GCLK12_0

E10~IO_L37P_GCLK13_0

GND

M12~IO_L2P_CMPCLK_2

R12~IO_L52P_M1DQ14_1

17

18

F9~IO_L40P_0

B12~IO_L62P_0

A12~IO_L62N_VREF_0

2,5V

2,5V

M11~IO_L2N_CMPMOSI_2

18

19

D9~IO_L40N_0

A9~IO_L34N_GCLK18_0

C9~IO_L34P_GCLK19_0

1,2V

T12~IO_L52N_M1DQ15_1

M10~IO_L16N_VREF_2

19

20

A8~IO_L33N_0

C8~IO_L38N_VREF_0

D8~IO_L38P_0

P8~IO_L30P_GCLK1_D13_2

R9~IO_L23P_2

T9~IO_L23N_2

20

21

B8~IO_L33P_0

GND

GND

M9~IO_L29P_GCLK3_2

N9~IO_L14P_D11_2

P9~IO_L14N_D12_2

21

22

E8~IO_L36N_GCLK14_0

VCCO_IO

VCCO_IO

T7~IO_L32N_GCLK28_2

N8~IO_L29N_GCLK2_2

T8~IO_L30N_GCLK0_USERCCLK_2

22

23

E7~IO_L36P_GCLK15_0

1,2V

1,2V

M7~IO_L31N_GCLK30_D15_2

P7~IO_L31P_GCLK31_D14_2

R7~IO_L32P_GCLK29_2

23

24

A7~IO_L6N_0

C7~IO_L6P_0

N6~IO_L64N_D9_2

P6~IO_L47P_2

T6~IO_L47N_2

24

25

E6~IO_L5N_0

F7~IO_L5P_0

M6~IO_L64P_D8_2

P4~IO_L63P_2

T4~IO_L63N_2

25

26

C6~IO_L7N_0

D6~IO_L7P_0

GND

GND

26

27

A6~IO_L4N_0

B6~IO_L4P_0

27

28

C5~IO_L3N_0

D5~IO_L3P_0

1,2V

1,2V

28

29

A5~IO_L2N_0

B5~IO_L2P_0

2,5V

TDI

29

30

A4~IO_L1N_VREF_0

C4~IO_L1P_HSWAPEN_0

TMS

30

31

VCCO_IO

VCCO_IO

TCK

31

32

GND

GND

GND

TDO

32

| Zusammenfassung | ||||

| A/B/E | C/D/F | |||

| FPGA-IO | 42 | FPGA-IO | 40 | |

| Serial | 2 | FX2-IO | 8 | |

| I2C | 2 | Wakeup | 1 | |

| Timer | 3 | JTAG | 4 | |

| Interrupt | 1 | Interrupt | 1 | |

| Breakpoint | 1 | USB 5V | 2 | |

| GND | 8 | GND | 7 | |

| 3,3V | 4 | 3,3V | 2 | |

| 1,2V | 4 | 1,2V | 3 | |

| 2,5V | 2 | 2,5V | 3 | |

| VCCO_IO | 4 | 5V | 3 | |

| 4..35V | 2 | NC | 6 | |

| NC | 5 | |||

| FPGA-GPIO | 42 | FPGA-GPIO | 40 | |

| SIO (spezial-I/O) | 9 | FX2-GPIO | 8 | |

| Power | 24 | SIO (spezial-I/O) | 6 | |

| NC | 5 | Power | 20 | |

| Summe | 80 | NC | 6 | |

| Summe | 80 | |||

Bilder

Klicken Sie auf die Bilder für vergrößerte Versionen.

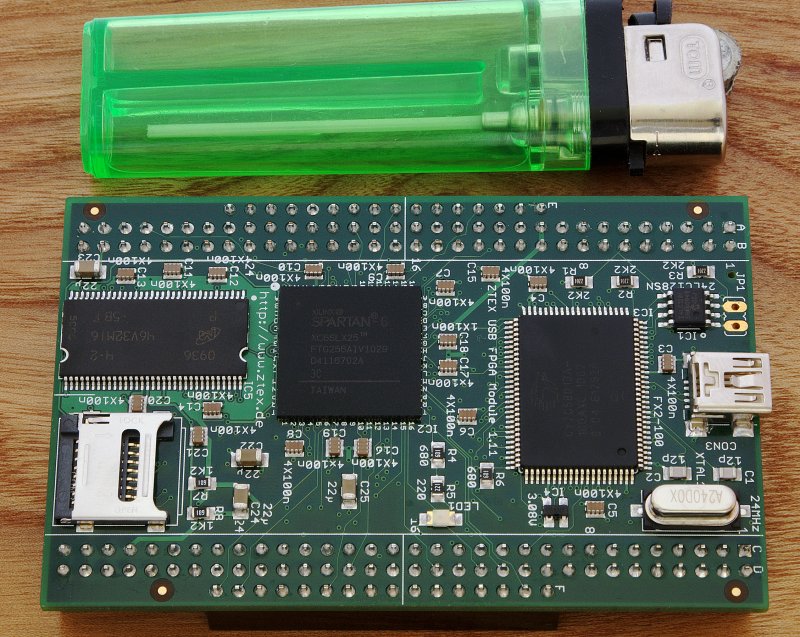

Größenvergleich des Spartan 6 USB-FPGA-Moduls 1.11c mit auf der Unterseite installierten Buchsenleisten. |

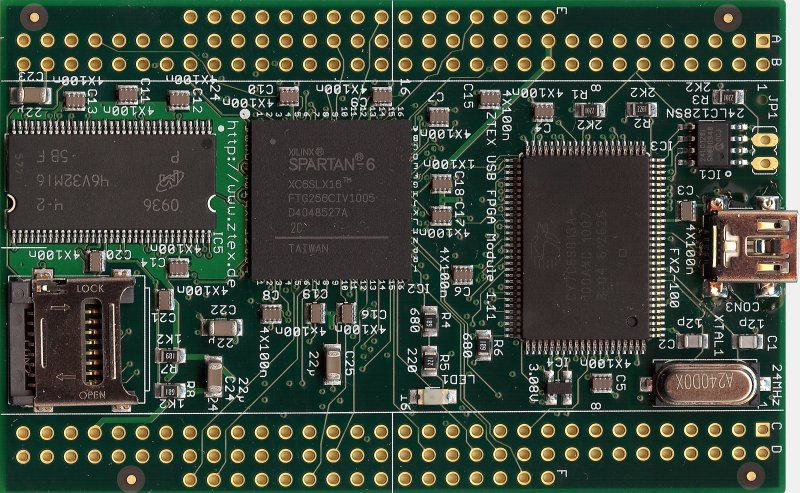

Oberseite des Spartan 6 USB-FPGA-Moduls 1.11b. |