USB-FPGA-Modul 1.15:

Spartan 6 LX45, LX75 und LX150 FPGA-Board mit USB 2.0-Mikrocontroller und 128 MByte DDR2 SDRAM

USB-FPGA-Module 1.15 sind veraltet. Bitte wechseln Sie zu FPGA Boards der Serie 2.

Als Übergangslösung ist ein Adapter verfügbar.

Die alte Produktseite ist hier weiterhin zu Dokumentationszwecken verfügbar.

|

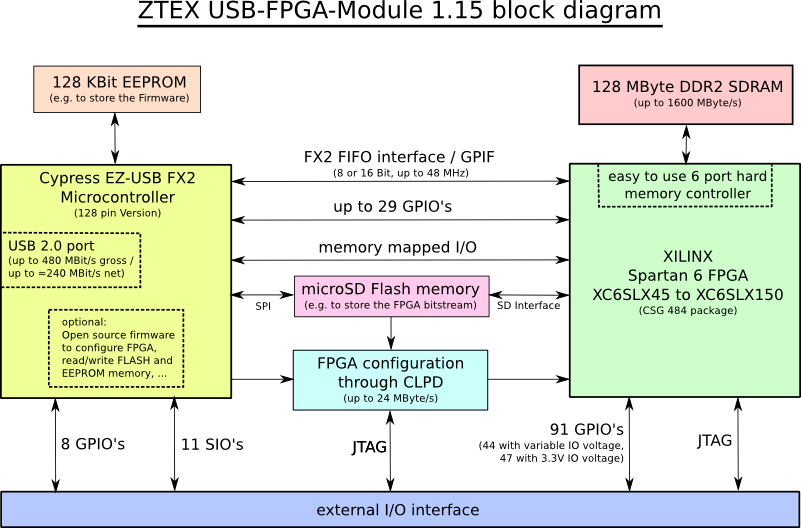

Blockdiagramm

Schaltplan (PDF) |

|

Blockdiagramm

Eigenschaften

- High-Speed (480 MBit/s) USB-Interface via Mini-USB-Buchse (Typ B)

- Cypress CY7C68013A EZ-USB FX2 Mikrocontroller

- Vier Xilinx Spartan 6 Varianten: LX45 (XC6SLX45), LX75 (XC6SLX75), LX100 (XC6SLX100) und LX150 (XC6SLX150), siehe Varianten

-

99 General Purpose I/O's (GPIO):

- 91 FPGA GPIO's

- 8 EZ-USB FX2 GPIO's

-

15 spezial-I/O's (SIO):

- 4 Pins für die FPGA-Konfiguration via JTAG

- 2 Pins für serielle Schnittstellen

- 2 Pins I2C-Interface

- 2 Interrupt-Pins

- 3 Timer

- 1 Wakeup-Pin

- 1 Breakpoint-Pin

-

128 MByte DDR2 SDRAM:

- Bis zu 400 MHz Taktfrequenz

- 16 Bit Busbreite

- Bis zu 1600 MByte/s Datenrate

- Einfach zu nutzender Hardware-Speichercontroller mit 6 Ports integriert im Spartan 6 FPGA. (siehe SDK für Beispiele)

- MicroSD-Sockel für erweiterbaren Flash-Speicher (normaler und hohe Kapazität (SDHC), Karten müssen SPI-Modus unterstützen)

-

Schnelle FPGA Konfiguration mittels CPLD:

- Bis zu 24 MByte/s via USB

- Bis zu 2.5 MByte/s vom microSD Flash (hängt von der Kartengeschwindigkeit ab)

- Memory-Mapped I/O zwischen EZ-USB FX2 und FPGA

- 128 Kbit EEPROM-Speicher (kann zum Laden der Firmware genutzt werden)

- 2 Kbit MAC-EEPROM: enthält eindeutige, nicht löschbare MAC-Adresse

- Externe Stromversorgung erforderlich:

- 3,3 V; Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: ≥ 800 mA

- 2,5 V - 2,6 V: Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: ≥ 300 mA

- 1,2 V; Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), siehe Varianten-Tabelle für empfohlene Minima

- Variable I/O-Spannung VCCO_IO: 1,14...3,46 V; Versorgungsstrom anwendungsabhängig (siehe Spartan 6-Datenblätter), empfohlen: ≥ 500 mA

- Kühlkörper für High-Performance- / Hochgeschwindigkeits-Anwendungen, siehe Abschnitt Kühlkörper

- Kein Löten erforderlich: Buchsenleisten auf der Unterseite (zwei 2x32 und zwei 1x23)

- Temperatur-Bereich: 0-70°C (-25°C - 85°C auf Anfrage)

- FPGA-Konfiguration / -Programmierung via USB mittels des EZ-USB FX2 SDK. (Keine JTAG-Adapter oder andere zusätzliche Hilfsmittel erforderlich.)

- FPGA-Konfiguration / -Programmierung vom Flash-Speicher

Varianten

Es werden Varianten mit unterschiedlicher Ausstattung angeboten.

| Variante | FPGA | Speedgrade (größer bedeutet schneller) |

Empfohlener Mindeststrom der 1.2V-Versorgung |

Max. Speichertakt / -Bandbreite |

Verfügbarkeit |

| USB-FPGA-Modul 1.15a | XC6SLX45 | 2 | 1800 mA | 333 MHz / 1333 MByte/s | Ausverkauft, wechseln Sie zu FPGA Boards der Serie 2 |

| USB-FPGA-Modul 1.15b | XC6SLX75 | 3 | 3000 mA | 400 MHz / 1600 MByte/s | |

| USB-FPGA-Modul 1.15c | XC6SLX100 | 3 | 4000 mA | 400 MHz / 1600 MByte/s | |

| USB-FPGA-Modul 1.15d | XC6SLX150 | 3 | 6000 mA | 400 MHz / 1600 MByte/s |

Andere Varianten (mit oder ohne Buchsenleisten, andere Speedgrades, erweiterter Temperatur-Bereich) können auf Anfrage produziert werden. Das LX75 FPGA Board (1.15b) ist die größte Variante, welche von der kostenlosen ISE Webpack-Version unterstützt wird. Die LX100 und LX150 Varianten benötigen eine kostenpflichtige Lizenz oder eine 30 Tage Test-Lizenz.

SDK, Beispiele, Tutorials

Für das USB-FPGA-Board steht ein quelloffenes Firmware-Entwicklungskit mit plattform-unabhängiger Hostsoftware API zur Verfügung. Dieses SDK erlaubt die Festlegung der USB-Geräte-Deskriptoren mit nur wenigen Makro-Kommandos und ermöglicht so dem Entwickler einen schnellen Einstieg in die Firmware Programmierung.Das SDK-Paket enthält eine Vielzahl von Beispielen welche als Ausgangspunkt für eigene Entwicklungen genutzt werden können.

Für mehr Informationen wird auf Abschnitt EZ-USB FX2 SDK verwiesen.

Weitere Dokumentationen einschließlich Tutorials befinden sich auf der ZTEX Wiki.

Funktions-Beschreibung

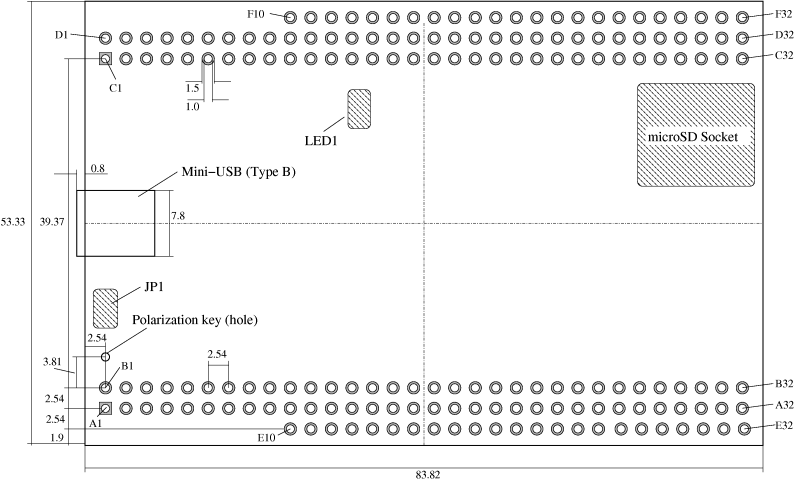

Die folgende Zeichnung zeigt die Maße sowie die Lage der beschriebenen Elemente.

Klicken sie auf das Bild für eine größere Version oder laden Sie die PDF-Version herunter.

FPGA-Konfiguration

Es gibt drei Möglichkeiten das FPGA zu konfigurieren:- Vom USB. Das kann entweder mittels API (siehe configureFpga) oder mittels FWLoader oder dem DeviceServer erfolgen. Der DeviceServer ermöglicht den bequemem Zugriff auf das FPGA-Board mittels HTTP-Interface und Webbrowser als GUI.

- Via JTAG, siehe JTAG-Abschnitt unten. Das Hochladen des Bitstreams auf große FPGA's (wie XC6SLX150) via JTAG kann ziemlich lange dauern. Deshalb sollte die USB-Methode bevorzugt werden.

- Vom microSD-Speicher, siehe Standalone-Beschreibung auf der ZTEX Wiki.

EEPROM-Adresse: JP1

Jumper JP1 legt die I2C-Adresse des EEPROM wie folgt fest:

| JP1 | I2C-Adresse |

| offen | 0xA2 |

| geschlossen | 0xAA |

Der EZ-USB FX2 Mikrocontroller sucht die Firmware an der Adresse 0xA2, welches die Standard-Adresse ist (Jumper offen).

Der Hauptzweck des Jumpers ist die Deaktivierung des EEPROM-Boot-Laders. Falls z.B. der EEPROM mit einer defekten Firmware programmiert wurde, kann der Mikrocontroller mit der internen Standard-Firmware gestartet werden, wenn JP1 während des Einschaltens geschlossen ist.

JP1 hat einen nicht verbundenen Pin der zum Parken des Jumpers genutzt werden kann. Die folgenden Bilder zeigen alle möglichen Jumper-Positionen:

|

|

| JP1 offen | JP1 geschlossen |

FPGA-Status: LED1

LED1 zeigt den Konfigurations-Zustand des FPGA's wie folgt an:

| LED1 | FPGA |

| an | unkonfiguriert |

| aus | konfiguriert |

Taktquellen

Auf dem FPGA-Board sind zwei Taktquellen mit den FPGA verbunden: der Taktausgang des EZ-USB FX2, welcher normalerweise auf 48 MHz konfiguriert ist, und der Interface-Takt, welcher auf 30 MHz oder 48 MHz eingestellt werden kann. Aus diesen können mittels DCM's oder PLL's andere Takte im FPGA generiert werden.Zusätzliche Taktsignale können an die GCLK-Pins des I/O-Steckverbinders angeschlossen werden.

In den meisten Fällen sind die Onboard-Taktquellen ausreichend.

Konfigurations-Booster-CPLD

Das CPLD ermöglicht die schnelle FPGA-Konfiguration via USB (bis zu 24 MByte/s) und vom Flash (bis zu 2.5 MByte/s). Das CPLD belegt die Bits 0 und 3 von Port A des EZ-USB FX2.Für die schnelle Konfiguration via USB wird ein Ausgangs-Endpoint des EZ-USB FX2 benötigt. Die Firmware ermöglicht es, einen für benutzerdefinierte Kommunikation gedachten Endpoint (wieder-) zu verwenden. Wenn alle Endpoint-Puffer des EZ-USB FX2 für Eingangs-Endpoints benötigt werden, muss die FPGA-Konfiguration in normaler Geschwindigkeit (ca. 1 MByte/s) via Endpoint 0 erfolgen.

Die FPGA-Konfiguration vom Flash erfolgt im seriellen Modus mit einer Geschwindigkeit von 24 MHz. Wegen der Latenzen beim Laden der Sektoren beträgt die maximale Konfigurationsgeschwindigkeit ca. 2.5 MByte/s.

Das CPLD ist werksseitig programmiert. Eine Neu-Programmierung ist via JTAG möglich. Die Quell-Dateien und die jed-Datei können hier herunter geladen werden: usb-fpga-1.15-cpld.zip.

I/O-Verbinder

Zwei 2x32-Pin und zwei 1x23-Pin Steckverbinder mit 2,54mm-Raster liefern die I/O-Signale und werden für die Stromversorgung genutzt. Die Zeichnung zeigt die Position der Verbinder.

Der I/O-Verbinder der USB-FPGA-Module 1.15 ist mechanisch abwärtskompatibel zum I/IO-Verbinder der USB-FPGA-Module 1.11 und USB-FPGA-Module 1.2

In der Nähe des B1-Pins befindet sich eine Polarisierungs-Markierung in Form eines kleinen Loches, siehe Zeichnung. Um Beschädigung zu vermeiden muss die Polarisierungs-Markierung (Loch) aller miteinander verbundenen Boards gleich ausgerichtet sein.

JTAG

Das FPGA kann entweder über USB oder über JTAG konfiguriert werden. Die JTAG-Signale stehen an den Pins D29 bis D32 des I/O-Steckverbinders zur Verfügung. Beim Experimentier-Board und dem Stromversorgungs-Modul stehen die JTAG-Signale an einem 14 Pin-Steckverbinder zur Verfügung.

Wird das JTAG-Interface zum Konfigurieren des FPGA's verwendet, muss Bit 1 am Port A des EZ-USB FX2 Mikrocontrollers (=PROG_B am FPGA) auf High gesetzt werden. Die geschieht automatisch wenn eine mit den SDK entwickelte Firmware geladen ist.

Das JTAG-Interface kann auch zum Neu-Programmieren des CPLD genutzt werden.

Kühlkörper

Für Hochgeschwindigkeits-Anwendungen wird ein Kühlkörper benötigt.Die FPGA-Boards werden mit einem 18×18×10mm-Kühlkörper (XC6SLX45- und XC6SLX75-FPGA-Boards) oder einem 25×25×12,5mm-Kühlkörper (XC6SLX100- und XC6SLX150-FPGA-Boards) einschließlich zweier doppelseitig klebender Wärmeleitpads ausgeliefert. Um Schaden während des Versands zu vermeiden, werden die Kühlkörper nicht montiert ausgeliefert. Das empfohlenen Vorgehen bei der Montage und Demontage ist für die beiden Varianten unterschiedlich.

Montage-Empfehlung für 18×18mm-Kühlkörper (LX45- und LX75-FPGA-Boards)

- Entfernen Sie den Schutzfilm von einer Seite des Wärmeleitpads und kleben Sie es auf den Kühlkörper

- Wenn gewünscht: Schneiden Sie die überstehenden Kanten des Wärmeleitpads mit einer Schere oder einem scharfen Messer ab. (Das Wärmeleitpad ist ca. 2mm größer.)

- Entfernen Sie die verbleibende Schutzfolie vom Wärmeleitpad und positionieren Sie den Kühlkörper mit moderatem Druck auf dem FPGA

Montage-Anleitung für 25×25mm-Kühlkörper (LX100- und LX150-FPGA-Boards)

- Entfernen Sie den Schutzfilm von einer Seite des Wärmeleitpads und kleben Sie es mittig auf den Kühlkörper. Das Wärmeleitpad ist ca. 2mm größer als das FPGA. Daher muss die Positionierung nicht exakt erfolgen.

- Entfernen Sie die Schutzfolie von der anderen Seite des Wärmeleitpads und positionieren Sie den Kühlkörper mit moderatem Druck auf dem FPGA. Stellen Sie dabei sicher, dass genügend Abstand zum microSD-Sockel bleibt und C5 nicht berührt wird, wie nachfolgend abgebildet

falsch |

O.K. |

besser |

Demontage-Anleitung für 18×18mm-Kühlkörper (LX45- und LX75-FPGA-Boards)

18×18mm-Kühlkörper können sicher entfernt werden, indem mit einer dünnen Messerschneide der Kühlkörper an einer Ecke angehoben wird.

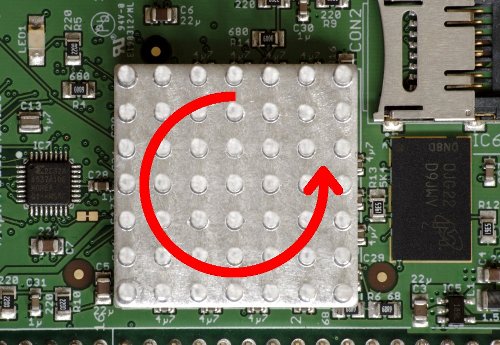

Demontage-Anleitung für 25×25mm-Kühlkörper (LX100- und LX150-FPGA-Boards)

Die Demontage von 25×25mm-Kühlkörpern ist schwierig und kann zu Beschädigungen am FPGA-Board führen. Der Kühlkörper darf nicht nach oben gezogen oder hochgehebelt werden. Der Kühlkörper lässt sich am sichersten durch Drehen, d.h. durch Scherkräfte ablösen, wie nachfolgend abgebildet.

Pinliste und Liste der Verbindungen

Die Pinliste des I/O-Verbinders und die Liste der Verbindungen können im Gnumeric- oder Excel-Format heruntergeladen werden. Diese Dateien beinhalten die Daten für alle USB-FPGA Boards einschließlich Kompatibilitätsinformationen. (Achtung: Die Dateien enthalten mehrere Blätter.)

Es folgt die Pinliste des I/O-Verbinders:

Pinliste

E

A

B

C

D

F

1

4..35V

4..35V

USB_5V

USB_5V

1

2

GND

GND

5V (unbenutzt)

5V (unbenutzt)

2

3

INT4

T0

L20~IO_L43P_GCLK5_M1DQ4_1

5V (unbenutzt)

3

4

T1

T2

GND

GND

4

5

BKPT

GND

INT5#

WAKEUP*

5

6

SCL

SDA

3.3V

3.3V

6

7

3.3V

3.3V

7

8

TxD0

RxD0

GND

V20~IO_L71N_1

8

9

A20~IO_L16N_1

A19~IO_L16P_1

PE7/GPIFADR8

Y22~IO_L59N_1

9

10

1.2V

2.5V

2.5V

PE6/T2EX

AA22~IO_L63N_1

AA21~IO_L63P_1

10

11

1.2V

1.2V

1.2V

PE5/INT6

Y21~IO_L59P_1

AB21~IO_L61N_1

11

12

VREF

A18~IO_L66N_SCP0_0

B18~IO_L66P_SCP1_0

PE4/RXD1OUT

W20~IO_L53P_1

Y20~IO_L67N_1

12

13

C16~IO_L65N_SCP2_0

D17~IO_L65P_SCP3_0

GND

PE3/RXD0OUT

AA20~IO_L61P_1

AB20~IO_L65N_1

13

14

B16~IO_L63P_SCP7_0

A17~IO_L64N_SCP4_0

C17~IO_L64P_SCP5_0

PE2/T2OUT

V19~IO_L71P_1

AB19~IO_L65P_1

14

15

A16~IO_L63N_SCP6_0

C14~IO_L46N_0

D15~IO_L46P_0

PE1/T1OUT

Y19~IO_L67P_1

AB18~IO_L2N_CMPMOSI_2

15

16

B12~IO_L36P_GCLK15_0

3.3V

3.3V

PE0/T0OUT

V18~IO_L73N_1

AA18~IO_L2P_CMPCLK_2

16

17

A12~IO_L36N_GCLK14_0

A11~IO_L35N_GCLK16_0

C11~IO_L35P_GCLK17_0

GND

Y15~IO_L5P_2

AA16~IO_L4P_2

17

18

B14~IO_L50P_0

C13~IO_L48P_0

A13~IO_L48N_0

2.5V

2.5V

AB15~IO_L5N_2

18

19

A14~IO_L50N_0

C12~IO_L37N_GCLK12_0

D11~IO_L37P_GCLK13_0

1.2V

V15~IO_L13N_D10_2

W14~IO_L16P_2

19

20

D12~IO_L47N_0_NC45

C15~IO_L62P_0

F10~IO_L38P_0

Y11~IO_L31P_GCLK31_D14_2

W15~IO_L14P_D11_2

Y16~IO_L14N_D12_2

20

21

D13~IO_L47P_0_NC45

GND

GND

AA12~IO_L30P_GCLK1_D13_2

AA14~IO_L15P_2

AB14~IO_L15N_2

21

22

A10~IO_L34N_GCLK18_0

VCCO_IO

VCCO_IO

Y10~IO_L29N_GCLK2_2

AB12~IO_L30N_GCLK0_USERCCLK_2

AB11~IO_L31N_GCLK30_D15_2

22

23

B10~IO_L34P_GCLK19_0

1.2V

1.2V

AB10~IO_L32N_GCLK28_2

AA10~IO_L32P_GCLK29_2

W11~IO_L29P_GCLK3_2

23

24

C9~IO_L8P_0

C10~IO_L33N_0

D10~IO_L33P_0

Y13~IO_L41P_2

T14~IO_L20P_2

U14~IO_L20N_2

24

25

C7~IO_L5P_0

D8~IO_L32N_0

D9~IO_L32P_0

W9~IO_L47P_2

W12~IO_L42P_2

Y12~IO_L42N_2

25

26

A7~IO_L5N_0

A8~IO_L6N_0

B8~IO_L6P_0

GND

GND

VREF

26

27

B6~IO_L4P_0

C8~IO_L7N_0

D7~IO_L7P_0

Y8~IO_L47N_2

27

28

VREF

C6~IO_L3N_0

D6~IO_L3P_0

1.2V

1.2V

AB7~IO_L63N_2

28

29

3.3V

A5~IO_L2N_0

C5~IO_L2P_0

2.5V

TDI

Y7~IO_L63P_2

29

30

3.3V

B3~IO_L1P_HSWAPEN_0

A6~IO_L4N_0

TMS

AB6~IO_L64N_D9_2

30

31

GND

VCCO_IO

VCCO_IO

TCK

AA6~IO_L64P_D8_2

31

32

GND

GND

GND

GND

TDO

VREF

32

| Zusammenfassung | ||||

| A/B/E | C/D/F | |||

| FPGA-IO | 46 | FPGA-IO | 45 | |

| Seriell | 2 | FX2-IO | 8 | |

| I2C | 2 | Wakeup | 1 | |

| Timer | 3 | JTAG | 4 | |

| Interrupt | 1 | Interrupt | 1 | |

| Breakpoint | 1 | USB 5V | 2 | |

| GND | 10 | GND | 7 | |

| 3.3V | 6 | 3.3V | 2 | |

| 1.2V | 6 | 1.2V | 3 | |

| 2.5V | 2 | 2.5V | 3 | |

| VREF_IO | 2 | VREF_3.3 | 2 | |

| VCCO_IO | 4 | 5V | 3 | |

| 4..35V | 2 | NC | 6 | |

| FPGA-GPIO | 46 | FPGA-GPIO | 45 | |

| SIO (Spezial-I/O) | 9 | FX2-GPIO | 8 | |

| Stromversorgung | 32 | SIO (Spezial-I/O) | 6 | |

| Stromversorgung | 22 | |||

| NC | 6 | |||

| Summe | 87 | Summe | 87 | |

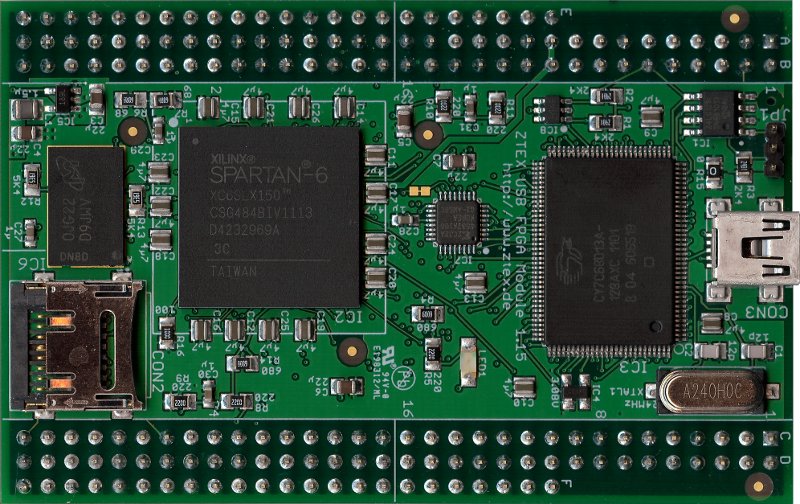

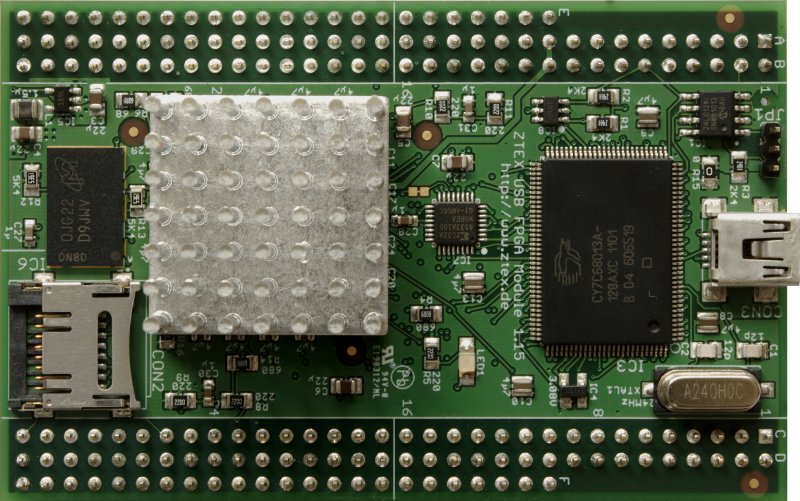

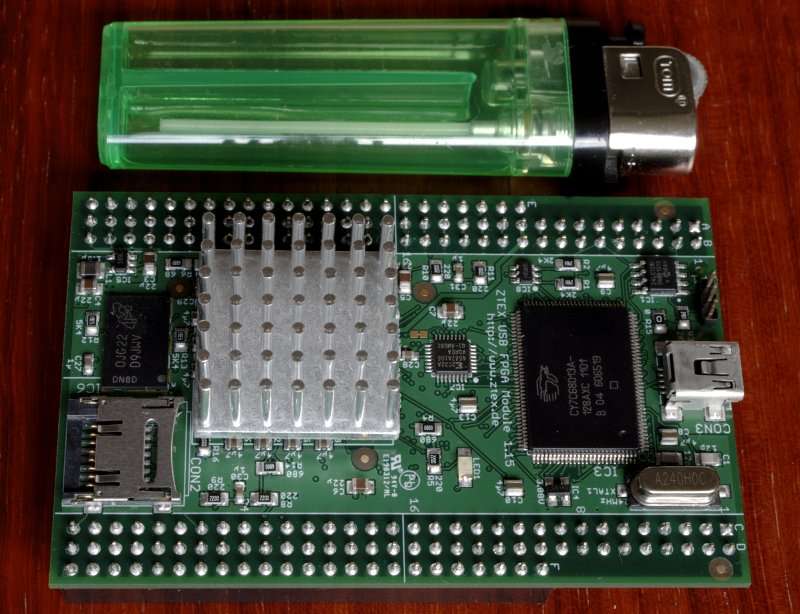

Bilder

Klicken Sie auf die Bilder für vergrößerte Versionen.

Oberseite des Spartan 6 USB-FPGA-Moduls 1.15d mit LX150 (XC6SLX150). Ebenfalls verfügbar mit LX45 (1.15a, XC6SLX45), LX75 (1.15b, XC6SLX75) und LX100 (1.15c, XC6SLX100). |

USB-FPGA-Modul 1.15 mit 18×18mm-Kühlkörper. Diese Kühlkörper werden mit der LX45- (1.15a, XC6SLX45) und LX75-Variante (1.15b, XC6SLX75) der FPGA-Boards geliefert. |

USB-FPGA-Modul 1.15 mit 25×25mm-Kühlkörper. Diese Kühlkörper werden mit der LX100- (1.15c, XC6SLX100) und LX150-Variante (1.15d, XC6SLX100) der FPGA-Boards geliefert. |

Größenvergleich des Spartan 6 USB-FPGA-Moduls 1.15. Diese FPGA-Boards sind in vier Varianten verfügbar: 1.15a (LX45 / XC6SLX45), 1.15b (LX75 / XC6SLX75), 1.15c (LX100 / XC6SLX100) und 1.15d (LX150 / XC6SLX150). |