ZTEX FPGA-Boards der Serie 2

ZTEX USB-FPGA-Module 2.∗ bilden eine Serie von FPGA-Boards mit USB-Controller und einem kompatiblen externen I/O-Steckverbinder. Diese Seite beschreibt die gemeinsamen Eigenschaften und gibt einen Überblick über die FPGA-Boards und das Zubehör.

FPGA-Boards - Produktübersicht

Zubehör

Gemeinsame Eigenschaften

SDK, Beispiele und Einführungen

Beschreibung gemeinsamer Funktionen

Laden der Firmware

FPGA-Konfiguration

Möglichkeiten zum Hochladen von Firmware und Bitstream

Externer I/O-Steckverbinder

Pinbelegung und -Beschreibung

Kompatibilität

Nummerierungsschema

FPGA-Boards - Produktübersicht

|

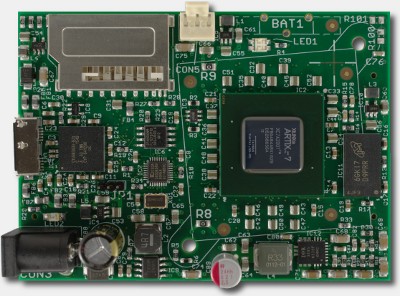

USB-FPGA-Modul 2.18

|

|

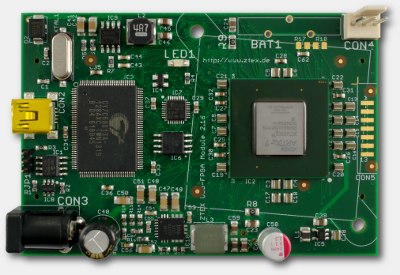

USB-FPGA-Modul 2.16

|

|

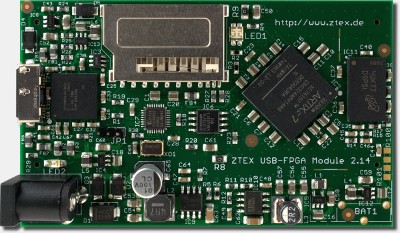

USB-FPGA Module 2.14

|

|

USB-FPGA-Modul 2.13

|

|

USB-FPGA-Modul 2.01

|

|

FPGA-Modul 2.00

|

Eingestellt: |

|

|

USB-FPGA-Modul 2.04

|

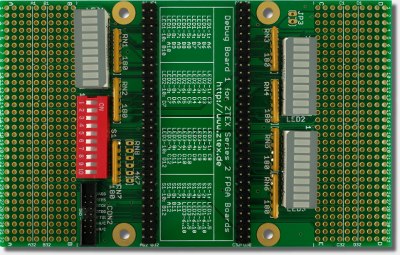

Zubehör

|

Debug-BoardEine Erweiterungskarte mit vielen LED's, Schaltern und einem JTAG-Verbinder. Es vereinfacht das Debuggen und die Prototypenentwicklung und ist in zwei Varianten erhältlich:

|

|

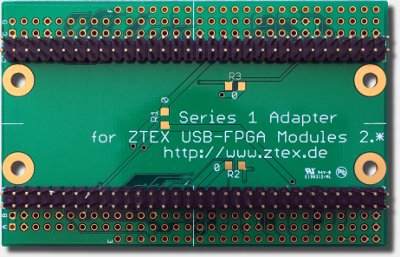

Serie-1-AdapterEine Adapter-Platine welche es ermöglicht FPGA-Boards der Serie 2 auf Anwendungs-Schaltungen für USB-FPGA-Module 1.∗ zu betreiben. Die Platine kann auch als Montageadapter verwendet werden, falls keine Anwendungs-Schaltung vorhanden, auf die das FPGA-Board gesteckt erden kann. |

|

Cluster-BasisplatineVerbindet bis zu 4 FPGA-Boards der Serie 2 zu einem kleinem Cluster-Knoten. |

|

Mehr Zubehör befindet sich im ZTEX-Shop |

Gemeinsame Eigenschaften

- Externer I/O-Steckverbinder mit:

- Bis zu 100 mit dem FPGA verbundene General-Purpose-I/O's (GPIO)

- JTAG-Signalen

- Reset-Signal

- Eingang für externe Stromversorgung

- 3.3V-Ausgang

- Eingang oder Ausgang für I/O-Spannung

- On-Board Stromversorgung

- On-Board SPI-Flash-Speicher zum Speichern des Bitstreams

- On-Board EEPROM oder Flash zum Speichern des Firmware

- On-Board MAC-EEPROM: enthält eine eindeutige, nicht löschbare MAC-Adresse und wird zum Speichern von Firmware-Einstellungen genutzt

- Unterstützung von SD-Karten als sekundärer Flash, siehe ZTEX Wiki

- SDK welches sowohl das FPGA-Board als auch den Host-PC abdeckt

SDK, Beispiele und Einführungen

Alle ZTEX USB-FPGA Module werde durch das ZTEX SDK unterstützt. Dieses ist für EZ-USB FX2- und FX3-Mikrocontroller entwickelt und beinhaltet Firmware Kits, eine Host-Software-API, Werkzeuge und viele Beispiele.Eine Standard-Firmware mit flexibler Kommunikations-Schnittstelle macht die Firmware-Entwicklung bei vielen Anwendungen überflüssig und erlaubt Board-unabhängige Host-Software.

Zusätzliche Dokumentationen einschließlich Einführungen befinden sich auf der ZTEX Wiki

Im Rahmen der FX3-Portierung wird das SDK gegenwärtig (Anfang 2016) umgebaut. Der Entwicklungsfahrplan befindet sich auf der FX3 Portierungs-Seite.

Beschreibung gemeinsamer Funktionen

Funktionen, die für alle FPGA-Boards der Serie 2 gleich sind, werden hier beschrieben.Laden der Firmware

Der EZ-USB kann Firmware von zwei Quellen laden,- vom USB und

- aus dem nichtflüchtigen Speicher (FX2: EEPROM, FX3: Flash).

Alle FPGA-Bords der Serie 2 haben den Jumper JP1, mit welchem das Laden der Firmware aus dem nichtflüchtigen Speicher deaktiviert werden kann. Dies ist vor allem nützlich, falls eine defekte Firmware installiert wurde. Details werden auf den FPGA-Board spezifischen Seiten beschrieben.

FPGA-Boards der Serie 2 werden mit einer ab Werk installierten Standard-Firmware geliefert, welche mit Nutzer-Firmware überschrieben werden kann, siehe Möglichkeiten zum Hochladen von Firmware und Bitstream.

FPGA-Konfiguration

Es gibt drei Möglichkeiten zur FPGA-Konfiguration:- Via USB mittels des SDK

- Via JTAG mit Hilfe der Xilinx-Werkzeuge (Kann sehr langsam sein. USB ist deshalb zu bevorzugen.)

- Vom Flash mittels des SDK

Falls ein Bitstream in den Flash-Speicher geschrieben wurde, versucht die Firmware automatisch diesen während des Hochfahrens in das FPGA zu laden.

Alle FPGA-Boards der Serie 2 haben ein LED welche den Konfigurations-Zustand des FPGA's anzeigt. Details befinden sich auf den FPGA-Board spezifischen Seiten.

Möglichkeiten zum Hochladen von Firmware und Bitstream

Das SDK bietet mehrere Möglichkeiten Firmware und Bitstream direkt zum EZ-USB bzw. FPGA oder in den nichtflüchtigen Speicher zu laden:- API:

- uploadFirmware um Firmware in den EZ-USB zu laden

- nvUploadFirmware um Firmware in den nichtflüchtigen Speicher zu laden

- configureFpga um den Bitstream in das FPGA zu laden

- flashUploadBitstream um den Bitstream in den nichtflüchtigen Speicher zu laden

- Kommandozeilen-Werkzeug FWLoader

- Server basierte (G)UI DeviceServer

Externer I/O-Steckverbinder

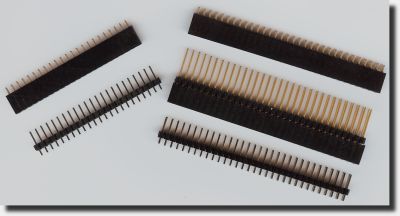

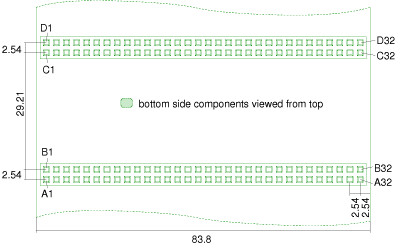

Der externer I/O-Steckverbinder befindet sich auf der Unterseite und besteht aus zwei 2x32 Steckverbindern mit 2.54mm-Raster.

Zeichnung mit Maßen des externen I/O-Verbinders der FPGA-Board-Serie 2. (Klicken Sie auf das Bild für eine PDF-Version.) |

Externer I/O-Verbinder auf der Unterseite des Artix 7 USB-FPGA-Moduls 2.16. (Klicken Sie auf das Bild für eine größere Version.) |

Pinbelegung und -Beschreibung

Die Pin-Belegung und -beschreibung kann auch im Gnumeric- oder Excel-Format heruntergeladen werden (mehrere Blätter). Diese Tabellen enthalten auch FPGA-Board-spezifische Details wie Verbindungslisten (Netzlisten) und I/O-Spannungs-Bereiche.Eine Eagle-Bibliothek ist ebenfalls verfügbar.

|

|

Kompatibilität

Die im vorherigen Abschnitt genannte Pinbelegung ist zwar für alle FPGA-Board der Serie 2 festgelegt, jedoch sind nicht in jedem Fall alle Pins bzw. Funktionen belegt. Um Die Wahrscheinlichkeit von Inkompatibilitäten bei der Migration zwischen FPGA-Boards zu vermeiden, sollten einige Regeln berücksichtigt werden:- Spezielle IO-Funktionen wie differentielle Signale oder Takt-Pins sollten vermieden werden (stattdessen die internen Taktquellen verwenden)

- Nicht immer sind alle FPGA-IO's belegt. Gegenwärtig betrifft das nur USB-FPGA-Module 2.04 und wahrscheinlich werden zukünftige FPGA-Boards voll belegt sein. Die FPGA-IO's mit niedrigen Nummern sollten möglichst vermeiden werden.

- Nicht immer ist die IO-Spannung aller FPGA-IO's variabel. Gegenwärtig betrifft das nur USB-FPGA-Module 2.04 und wahrscheinlich wird bei zukünftigen FPGA-Boards die Spannung aller FPGA-IO's variabel sein. Wenn möglich, sollte eine IO-Spannung von 3.3V gewählt werden.

- Die Pins mit mittleren Nummern haben die besten Signal-Laufzeiten

Nummerierungsschema

Das Nummerierungsschema für die FPGA-Boards ist 2.<n><m>, z.B. 2.16.| 2. | Seriennummer: Ist immer 2. |

| <n> | FPGA-Generation: |

| <m> | Board-Nummer: Eine größere Zahl bedeutet gewöhnlich ein größeres FPGA-Board in irgend einem Sinn, z.B. größeres FPGA, mehr Speicher, besserer USB-Controller. |